TSMC recently held their Open Innovation Platform (OIP) Ecosystem Forum event where many of their key partners presented on their latest projects and developments. This year one of their top IP provider partners, Analog Bits, gave two presentations. Analog building blocks have always been necessary as enabling technology … Read More

Author: Tom Simon

On-Chip Sensors Discussed at TSMC OIP

Optical I/O Solutions for Next-Generation Computing Systems

According to DARPA the fraction of total power consumed in semiconductors for I/O purposes as been growing rapidly and is creating an I/O power bottleneck. It has reached the point where it needs to be addressed with new technologies and approaches. Interestingly, while the energy density, as measured by pJ/bit for short reach… Read More

Webinar on Protecting Against Side Channel Attacks

SoC design for security has grown and evolved over time to address numerous potential threat sources. Many countermeasures have arisen to deal with ways hackers can gain control of systems through software or hardware design flaws. The results are things like improved random number generators, secure key storage, crypto, and… Read More

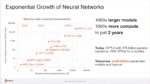

Neural Network Growth Requires Unprecedented Semiconductor Scaling

The truth is that we are just at the beginning of the Artificial Intelligent (AI) revolution. The capabilities of AI are just now starting to show hints of what the future holds. For instance, cars are using large complex neural network models to not only understand their environment, but to also steer and control themselves. For… Read More

Ansys Talks About HFSS EM Solver Breakthroughs

Ansys HFSS™ has long enjoyed industry respect as a highly accurate electromagnetic simulator suitable for general purpose applications. Ansys has worked over the years to maintain its gold reference accuracy, and also to dramatically improve its performance and ease of use. A very interesting review of the key technology breakthroughs… Read More

DARPA Toolbox Initiative Boosts Design Productivity

When you think of the Defense Advanced Research Projects Agency (DARPA), this first thing that comes to mind is the development of the internet. And indeed, if you look at their website’s historic timeline, the development of ARPANET, as it was known at the time, is shown prominently in 1969. Incidentally, I actually used one of … Read More

Heterogeneous Package Design Challenges for ADAS

Increasingly complex heterogeneous packaging solutions have proved essential to meeting the rapidly scaling requirements for automotive electronics. Perhaps there is no better example of this than advanced driver-assistance systems (ADAS) that are found in most new cars. In a recent paper published by Siemens EDA, they … Read More

Symmetry Requirements Becoming More Important and Challenging

Humans certainly have always had an aesthetic preference for symmetry. We also see symmetry showing up frequently in nature. The importance of symmetry in electronic designs has been apparent for decades. There are a host of analog structures that require balanced layout. For instance, these include differential pairs and … Read More

Cadence Tempus Update Promises to Transform Timing Signoff User Experience

Cadence invests heavily in the development of their Tempus Timing Signoff Solution due to its importance in the SoC design flow. I recently had a discussion on the topic of the most recent Tempus update with Brandon Bautz, senior product management group director in the Digital & Signoff Group, and Hitendra Divecha, product… Read More

Have STA and SPICE Run Out of Steam for Clock Analysis?

At advanced nodes such as 7 and 5nm, timing closure and sign off are becoming much more difficult than before at 16nm. One area of chips that has increased in complexity dramatically and who’s correct operation is essential for silicon success is the clock tree. If the clock tree has excessive jitter, it will throw off every timing… Read More

Tesla and Samsung Relationship Update