You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

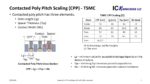

TSMC presented two papers on 3nm at the 2022 IEDM; “Critical Process features Enabling Aggressive Contacted Gate Pitch Scaling for 3nm CMOS Technology and Beyond” and “A 3nm CMOS FinFlexTM Platform Technology with Enhanced Power Efficiency and Performance for Mobile SOC and High Performance Computing Applications”.

When … Read More

Ann Kelleher is Intel’s Executive Vice President, General Manager, Technology Development, and she gave the first plenary talk to kick off the 2022 IEDM, “Celebrating 75 Years of the Transistor A Look at the Evolution of Moore’s Law Innovation”. I am generally not a fan of plenary talks because I think they are often too broad and… Read More

Recently TechInsights analyzed a Bitcoin Miner chip fabbed at SMIC and declared SMIC has a 7nm process. There has been some debate as to whether the SMIC process is really 7nm and what it means if it is 7nm. I wanted to discuss the case for and against the process being 7nm, and what I think it means.

First off, I want to say I am not going … Read More

SEMICON West 2022 was held from July 12th to 14th at the Moscone Center in San Francisco.

On Monday the 11th before the show, Imec held a technology forum at the Marriott Marquee right around the corner from the Moscone center. In recent years the Imec forums have shifted away from the process technology I cover to more of a system and… Read More

IEDM is one of the premiere conferences for the latest information on leading edge semiconductor technology. The 68th annual International Electron Devices Meeting will be held December 3rd through 7th at the San Francisco Hilton.

The paper submission deadline is July 14, 2022, and the late-news deadline is August 22, 2022. … Read More

At the VLSI Technology Symposium Imec presented on Buried Power Rails (BPR) and Backside Power Delivery (BSPD) in a paper entitled: “Scaled FinFETs Connected by Using Both Wafer Sides for Routing via Buried Power Rails”. I recently had a chance to interview one of the authors, Naoto Horiguchi about the work. I have interviewed … Read More

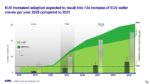

At the 2022 SPIE Advanced Lithography Conference, ASML presented an update on EUV. I recently had a chance to go over the presentations with Mike Lercel of ASML. The following is a summary of our discussions.

0.33 NA

The 0.33 NA EUV systems are the production workhorse systems for leading edge lithography today. 0.33 NA systems are… Read More

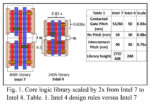

As I previously wrote about here, Intel is presenting their Intel 4 process at the VLSI Technology conference. Last Wednesday Bernhard Sell (Ben) from Intel gave the press a briefing on the process and provided us with early access to the paper (embargoed until Sunday 6/12).

“Intel 4 CMOS Technology Featuring Advanced FinFET Transistors… Read More

The VLSI Symposium on Technology & Circuits will be held in Hawaii from June 12th to June 17th. You can register for the conference here.

The tip sheet for the conference has been released and one thing that caught my eye is some data from the Intel 4 paper that Intel will be presenting at the conference.

Intel’s old roadmap had 14nm,… Read More

I spent several days this week at the SEMI International Strategy Symposium (ISS). One of the talks was “Can the Semiconductor Industry Reach $1T by 2030” given by Bob Johnson of Gartner. His conclusion was, that $1 trillion dollars is an aggressive forecast for 2030 but certainly we should reach $1 trillion dollars in the next 10… Read More

Intel Foundry: How They Got Here and Scenarios for Improvement