I could have written the sequence of the title in reverse order, but no, design is the one which initiates the need of a particular flow and the flow needs support of EDA tools to satisfy that need. It’s okay if the design is small; some manual procedures and workarounds/scripts may be able to perform certain jobs. However, as the design… Read More

Author: Pawan Fangaria

Power and Reliability Sign-off – A must, but how?

At the onset of SoCs with multiple functionalities being packed together at the helm of technologies to improve upon performance and area; power, which was earlier neglected, has become critical and needs special attention in designing SoCs. And there comes reliability considerations as well due to multiple electrical and … Read More

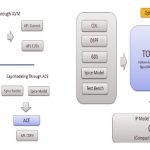

From Layout Sign-off to RTL Sign-off

This week, I had a nice opportunity meeting Charu Puri, Corporate Marketing and Sushil Gupta, V.P. & Managing Director at Atrenta, Noida. Well, I know Sushil since 1990s; in fact, he was my manager at one point of time during my job earlier than Cadence. He leads this large R&D development centre, consisting about 200 people… Read More

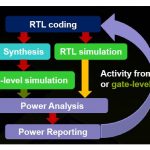

Efficient Power Analysis and Reduction at RTL Level

It’s a classic and creative example of design and EDA tool community getting together, exploiting tool capabilities and developing flows which add value to all stake holders including the end consumer. We know power has become extremely important for battery life in smart phones, high performance servers, workstations, notebooks… Read More

4th Fundamental Circuit Element – Can it be a boon to Semiconductor Industry?

It was a nice break after my vacation, indulging into some of the pure science stuff, when an old colleague of mine, Dr. Gaurav Gandhi, founder of mLabs in Delhi came across introducing me to his new research and possible developments in this field. Gaurav was actually in my product validation team while I was at Cadence, very passionate… Read More

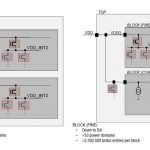

Increase Your Chip Reliability with iROC Tech

As we have moved towards extremely low process nodes with very high chip density, the cost of mask preparation also has become exorbitantly high. It has become essential to know about the failure rates and mitigate the same at the design time before chip fabrication, and also to make sure about chip reliability over time as it is constantly… Read More

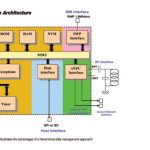

Hierarchical Design Management – A Must

Considering the technological progress, economical pressure, increased outsourcing and IP re-use, semiconductor industry is one of the most challenged industry today. Very frequently products get outdated leading to new development cycles. It becomes very difficult and costly to build the whole scheme of data foundation… Read More

SEMulator3D – A Virtual Fab Platform

Yes, it’s a pleasant surprise; it is Virtual Fabrication Platform, one of the new innovations in 2013. I was looking around for what kind of breakthrough technologies will be announced in DAC this year. And here I came across this new kind of innovative tool which can produce final virtual fabricated 3D structures after following… Read More

Do my tests certify the quality of my products?

Honestly speaking, there is no firm answer to this question, and often when we get confronted by our customers, we talk about the coverage reports. The truth is a product with high rate of coverage can very easily fail in customer environment. Of course coverage is important, and to be clear about the fact that the failure is not because… Read More

Design Data Management – Key Winning Strategy!

In a complex semiconductor market today, characterized by ever increasing design size and complexity, long design cycle, rapid technological advancement, intense competition, pricing pressure, small window of opportunity, development and cross-functional teams spread across the globe and multiple design partners including… Read More

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era