In an ever growing world of IPs, it’s essential that a tool which vouches to simplify designer’s job of IP development and help improving its quality remains versatile to encompass various formats, databases, common data models, standard libraries, scripting etc. that are used in the development of IPs and their exchange between… Read More

Author: Pawan Fangaria

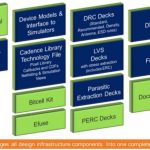

A Complete Scalable Solution for IP Signoff

In an SoC world driven by IP, where an SoC can have hundreds of IP (sourced not only from 3[SUP]rd[/SUP] party but also from internal business units which can have a lot of legacy) integrated together, it has become essential to have a comprehensive and standard method to verify and signoff the IP. Additionally, these checks must … Read More

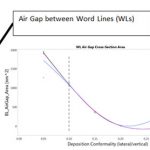

Proving the Power of Virtual Fabrication

There are many facets of our lives that are being driven to a more virtual method of doing things. This is largely due to issues such as scaling due to whatever reason – technical, business, economic. Let’s look at some general cases: In yesteryears people used to travel all the way for face-to-face meetings; today virtual meetings… Read More

StarVision to Debug and Analyze Designs at All Levels

In today’s SoC world where multiple analog and digital blocks along with IPs at different levels of abstractions are placed together on a single chip, debugging at all levels becomes quite difficult and clumsy. While one is working at the top level and needs to investigate a particular connection at an intermediate hierarchical… Read More

Key Collaboration to Enable Designs at Advanced Nodes

In the semiconductor ecosystem, several partners (or better to say stakeholders) join together in the overall value chain to finally output the most coveted chip, err I should say SoC these days. It becomes really interesting when we start analyzing the real value added by each of them, none appears to be less. Well, then to whom … Read More

What’s Behind Carbon System Exchange – How Will it Scale?

Earlier this year, when I was looking at Carbon’spast year performance which provided record breaking revenue with whopping jump in bookings, one thing was certain that Carbon Performance Analysis Kits (CPAKs) would drive major growth in future, not only for Carbon, but also for the semiconductor industry. It will initiate … Read More

ANSYS Tools Shine at FinFET Nodes!

In the modern semiconductor ecosystem we are seeing rapid advancement in technology breaking past once perceived limits; 28nm, 20nm, 16-14nm, 10nm and we are foreseeing 7nm now. Double and multi-patterning are already being seen along with complex FinFET structures in transistors to gain the ultimate advantages in PPA from… Read More

A Complete Timing Constraints Solution – Creation to Signoff

With the unprecedented increase in semiconductor design size and complexity design teams are required to accommodate multiple design constraints such as multiple power domains for low power design, multiple modes of operation, many clocks running, and third party IPs with different SDCs. As a result timing closure has become… Read More

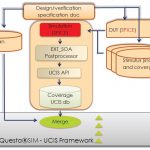

Coverage Driven Verification for Analog?

We know there is a big divide between analog and digital design methodologies, level of automation, validation and verification processes, yet they cannot stay without each other because any complete system on a chip (SoC) demands them to be together. And therefore, there are different methodologies on the floor to combine analog… Read More

Expansion at Calypto through Real Value Addition in SoC Design

When we get the notion of expansion of a company, it always provides a positive picture about something good happening to boost that expansion. There can be several reasons for expansion such as merger & acquisition, formation of joint venture or partnership, large customer orders and so on. However, organic expansion which… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center