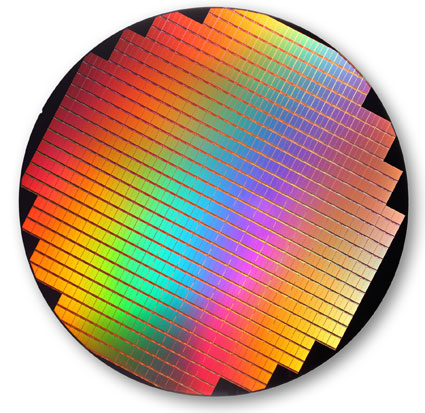

One of the most demanding areas of layout design has always been memories. Whereas digital design often uses somewhat simplified design rules, memories have to be designed pushing every rule to the limit. Obviously even a tiny improvement in the size of a bit cell multiplies up into significant area savings when there are billions… Read More

Author: Paul McLellan

Intel Buys an ARMy. Maybe

Is Intel in trouble? Since it is the #1 semiconductor company and, shipping 22nm in Q4 this year with 14nm in 2013, it is two process generations ahead of everyone else it is hard to see why it would be. Intel, of course, continues to dominate the market for chips for notebooks, desktops and servers. But therein lies the problem. Pads… Read More

Semiconductor Virtual Platform Models

Virtual platforms have been an area that has some powerful value propositions for both architectural analysis and for software development. But the fundamental weakness has been the modeling problem. People want fast and accurate models but this turns out to be a choice.

The first issue is that there is an unavoidable tradeoff… Read More

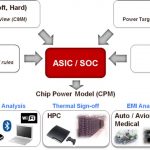

Chip-Package-System (CPS) Co-design

I can still remember the time, back in the mid-1980s, when I was at VLSI and we first discovered that we were going to have to worry about package pin inductance. Up until then we had been able to get away with a very simplistic model of the world since the clock rates weren’t high enough to need to worry about the package and PCB as… Read More

Andrew Yang’s presentation at Globalpress electronic summit

Yesterday at the Globalpress electronic summit Andrew gave an overview of the Apache product line, carefully avoiding saying anything he cannot due to the filing of Apache’s S-1. From a financial point of view the company has had 8 years of consecutive growth, is profitable since 2008, and has no debt. During 2010 when the… Read More

Process Design Kits: PDKs, iPDKs, openPDKs

One of the first things that needs to be created when bringing up a new process is the Process Design Kit, or PDK. Years ago, back when I was running the custom IC business line at Cadence, we had a dominant position with the Virtuoso layout editor and so creating a PDK really meant creating a Virtuoso PDK, and it was a fairly straightforward… Read More

RTL Power Analysis and Verification

“Power is the new timing” has almost become a cliché. There are a number of reasons for this, not least that increasingly it is power rather than anything else that caps the performance that a given system can deliver. Power is obviously very important in portable applications such as smartphones because it shows through directly… Read More

Apache files S-1

Apache Design Solutions today filed their S-1 with the SEC in preparation for its initial public offering (IPO). This is a big deal since there hasn’t been an IPO of an EDA company for may years (Magma was the last 10 years ago). As a private company they have not had to reveal their financials until now.

It turns out that they did… Read More

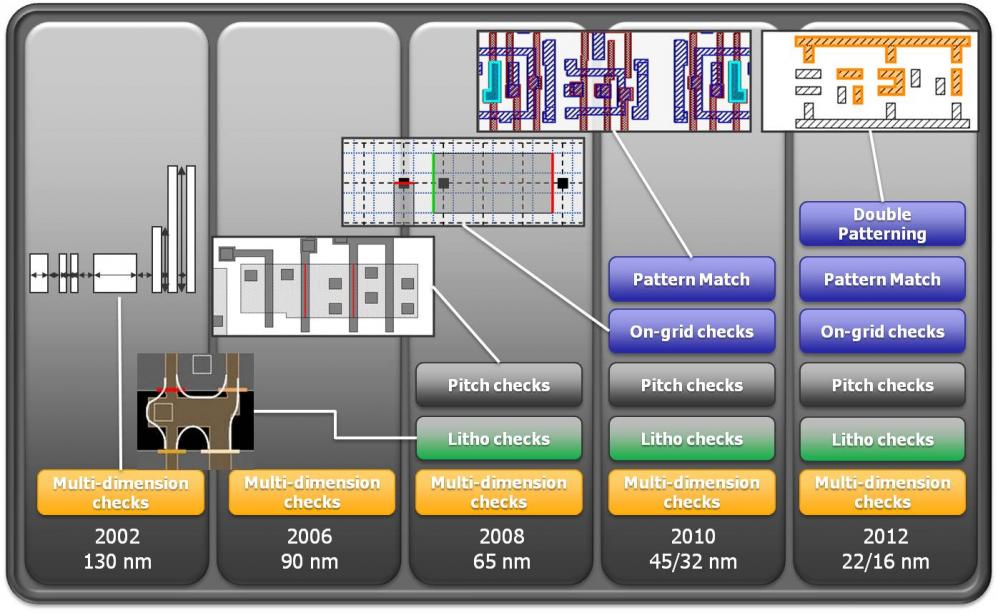

Checking AMS design rules instantly

With each process generation, the design rules get more and more complex. One datapoint: there are twice as many checks at 28nm as there are at 90nm. In fact, the complexity of the rules is outpacing the ability to describe them using the simplified approaches used in the DRCs built-into layout editors or formats like LEF.

Worse still,… Read More

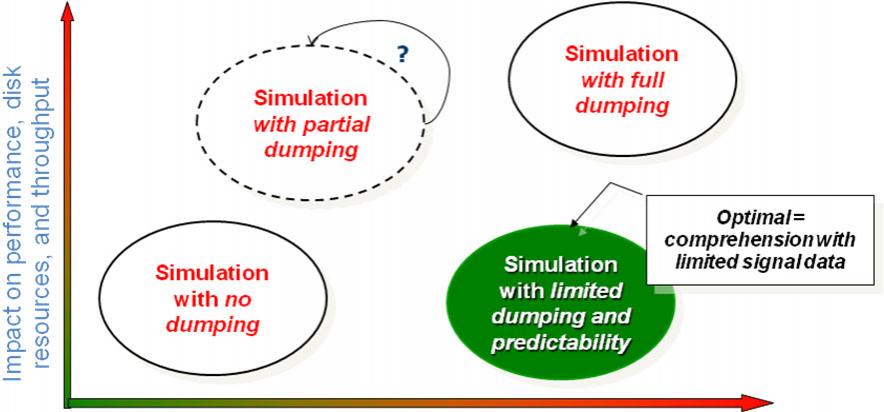

Essential signal data and Siloti

One of the challenges with verifying today’s large chips is deciding which signals to record during simulation so that you can work out the root cause when you detect something anomalous in the results. If you record too few signals, then you risk having to re-run the entire simulation when you omitted to record a signal that… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center