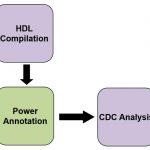

So far in my blog series on low power we’ve looked broadly at what’s changing in the low power verification landscape and focused on a new methodology developed by Mentor Graphics and ARM called successive refinement, which is now included in the UPF standard. Power management techniques create their own brand of clock domain crossing… Read More

Author: Ellie Burns

Syncing Up CDC Signals in Low Power Designs

Coming to a Workstation Near You: Accellera’s Portable Stimulus Standard

Portable Stimulus has become such a popular standards topic of late that I thought it would be good to take a break this month from my low power series to bring you, my valued readers, more information about it from one of my colleagues, Dennis Brophy, who is working to help drive development of this standard within Accellera. I’ll … Read More

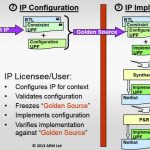

Shifting Low Power Verification to an IP to SoC Flow

One of the most exciting recent developments in low power design and verification is the successive refinement flow developed by ARM® and Mentor Graphics®.… Read More

Something Old, Something New…EDA and Verification

When I got the opportunity to blog about verification, I thought, what new and interesting things should I talk about? Having started my EDA career in 1983, I often feel like one of the “oldies” in this business…remember when a hard drive required a static strap, held a whopping 33 MB, and was the size of a brick? Perhaps they should … Read More

Siemens U2U 3D IC Design and Verification Panel