The state machine nature of many digital designs has made time-domain debugging the favorite tool for most designers. We provide a set of inputs, data gets clocked in, and a set of outputs appears. We look for specific patterns in parallel paths, or sequences on serial lines.… Read More

Author: Don Dingee

When the lines on the roadmap get closer together

Tech aficionados love roadmaps. The confidence a roadmap instills – whether using tangible evidence or just a good story – can be priceless. Decisions on “the next big thing”, sometimes years and a lot of uncertain advancements away, hinge on the ability of a technology marketing team to define and communicate a roadmap.

Any roadmap… Read More

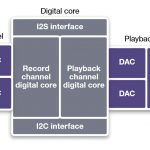

Shrinking audio creates issues and opportunities

There is a lot more to sound than meets the ear, and there a vast number of ways to deliver an audio experience. I recently trashed my gaming headset, replacing it with a Samson C03U mic and Audio-Technica ATH-PRO700MK2 headphones. It’s a huge upgrade, especially for podcasting, and I admit I was also motivated by research into digital… Read More

Is debugging a task, or a continuous process?

Early in my so-called EE career, I sat in a workshop led by the director of quality for the Ford truck plant in Louisville, KY, where “Quality is Job #1.” At that time, they were gaining experience in electronic control modules (ECMs) for fuel efficiency and emissions control. Who better to transfer the secrets of Crosby and Deming… Read More

SHIELDing the Android GPU developer in C

Repeat after me: SoCs are paperweights if they can’t be programmed. Succeeding with a new part today means supporting a robust developer program to attract and engage as many creatives as possible. NVIDIA has teamed up with Mentor Graphics in just such an adventure. If you read just the press release, you may have missed the real … Read More

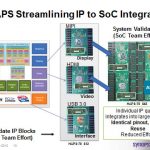

UVM: Lowering the barrier to IP reuse

One of my acquaintances at Intel must have some of the same viewing habits I do, based on a recent Tweet he sent. He was probably watching “The Men Who Built America” on the History Channel and thinking as I have a lot recently about how the captains of industry managed to drive ideas to monopolies in the late 1800s and early 1900s.

… Read MoreDifference

Help, my IP has fallen and can’t get up

We’ve been talking about the different technologies for FPGA-based SoC prototyping a lot here in SemiWiki. On the surface, the recent stories all start off pretty much the same: big box, Xilinx Virtex-7, wanna go fast and see more of what’s going on in the design. This is not another one of those stories. I recently sat down with Mick… Read More

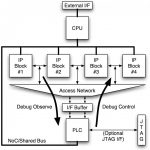

Seeing inside SoC designs, from the beginning

Engineers have this fascination with how things work. They are thrilled to tear stuff apart, and sometimes to even be able to put it back together afterwords. So I can keep my recovering engineer card, I thought I’d take a few moments and look inside a technology Daniel Payne and I have been covering here, exploring where the idea started… Read More

Time in a model: xtUML and concurrency

Most embedded programming strategies involve decomposing the embedded application into chunks, which can then be executed as independent tasks. More advanced applications involve some type of data flow, and may attempt to execute operations in parallel where possible.… Read More

You may want to check that known-good RTL

In his blog Coding Horror, Jeff Atwood wrote: “Software developers tend to be software addicts who think their job is to write code. But it’s not. Their job is to solve problems.” Whether the tool is HTML, C, or RTL, the reality is we are now borrowing or buying more software IP than ever, and integrating it into more complex designs,… Read More

Captain America: Can Elon Musk Save America’s Chip Manufacturing Industry?