You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

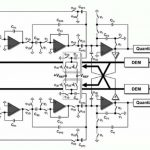

Switched-capacitor circuits are used in most CMOS mixed-signal ICs as:

- Track and hold circuits

- Integrators

- Operational Amplifiers

- Delta-sigma modulators

Delta-Sigma Modulator: IEEE J. Solid-State Circuits, vol. 43, no. 12, pp 2601-2612, Dec. 2008… Read More

You can often tell how important blogging and social media is to an EDA company by how much effort it takes to find their blog from the Home page. For the folks at Mentor Graphics I’d say that blogging is quite important, because it shows up as a top-level menu item. Notice also how important Twitter is, their latest tweets show… Read More

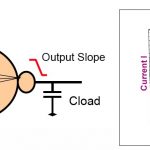

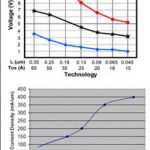

Semiconductor IP re-use enables modern SoC designs to be realized in a timely fashion, yet with hundreds of IP blocks in a chip the chances are higher that an error in any IP block could cause the entire system to fail. At advanced nodes like 28nm and smaller, the number of Process, Voltage and Temperature (PVT) corners is increasing… Read More

SoC designers are attracted to ARM as an IP provider because of their popular offerings and growing ecosystem of EDA partners like Carbon Design Systems. At the upcoming ARM Techcon on October 31 this week in Santa Clara you’ll have an opportunity to hear a joint presentation from ARM and Carbon Design Systems on: Getting … Read More

EDA and Semiconductor companies are offering new webinars almost every week of the year, so there’s always something worth learning about that only takes an hour of time. On November 5th there’s an interesting webinar planned on the topic of IP Lifecycle Management, hosted by Methodics. I blogged two weeks ago about,… Read More

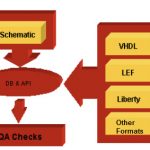

Imagine that you’re working in a CAD group and just received a new library of a few hundred IP blocks and you needed to know if these blocks conform to your design and quality standards. There are many questions about library and IP quality:

- Are all of the views consistent (layout, schematic, HDL, test, timing, SPICE)?

- Are there

…

Read More

Harish Aepalais part of the Design Closure Methodology group at LSIand he recently talked about his ASIC handoff experience in a webinar. Harish works with logic and physical synthesis, timing constraints, RTL analysis and formal verification.

One challenge with ASIC handoff has been getting through design closure with the… Read More

The company Nvidiais synonymous with designing all things video and GPU, so I watched Ting Ku, director of engineering at an archived webinar today talk about: Comprehensive Layout-based ESD Check Methodology with Fast Full-chip Static and Macro-level Dynamic Solutions.… Read More

18 months ago I blogged about how the mobile revolution that we enjoy today is really enabled by EDA software and IP in the hands of SoC designers, yet very few EDA and Semi IP companies had mobile-ready web sites. In that past 18 months we’ve witnessed only a handful of companies migrate to mobile-friendly web sites, the most… Read More

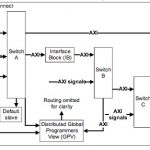

It’s common to see an SoC with a few hundred IP blocks today, which is quite a change from full-custom IC designs developed in the early days (i.e. 1980’s) where there was little IP re-use at all. This shift in the technology and business of IP has created a relatively new industry of IP providers from small to large in size.… Read More

Intel, Musk, and the Tweet That Launched a 1000 Ships on a Becalmed Sea