You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

Gary Smith published a list of what to see at DAC, and I noticed that he listed DOCEA Power in a category of ESL Thermal. I’ll be meeting the DOCEA engineers on Wednesday at DAC to learn more about their two newest ESL products:

- Thermal Profiler

- Power Intelligence

In general DOCEA Power tools allow you to manage power and thermal… Read More

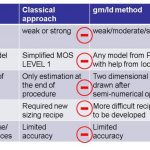

At DATEthis year in Dresden, Bernhard Fischer from Siemens CT(Corporate Technology) has presented an interesting summary of the various techniques used for power modeling and analysis at the architectural level. He went through the pros and cons of using spreadsheets, timed virtual platforms annotated with power numbers … Read More

The concept and use of virtual prototypes continues to grow each year in electronics design, mostly because it really does shorten product development cycles by allowing software engineers to start early debug and fix errors prior to production. Other useful benefits to virtual prototyping include software optimization, … Read More

Digital designers have used logic optimization and logic synthesis for decades as a means to produce more optimal designs with EDA tools. On the analog and transistor-level side of design the efforts to automatically optimize for speed or power have generally been limited to circuits with only a handful of transistors. These … Read More

I’m typing this blog today with my trusty Apple MacBook Pro – a 17″ laptop with matte display and 16GB of RAM, but don’t stereotype me as an Apple fanboy because I also own the fantastic Samsung Galaxy Note II phone (aka phablet). Some industry pundits would have us believe that desktops and laptops are going… Read More

IDM companies like Micronuse SPICE circuit simulators during the design phase in order to predict timing, currents and power on their custom IC chip designs at the transistor level. A senior memory design engineer at Micron named Raed Sabbahtalked today at a webinarabout how the embedded solutions group uses the FineSimcircuit… Read More

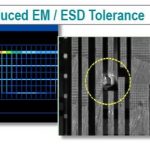

Reliability for ICs is a big deal because the last thing that you want to do is ship a new part only to find out later in the field that there are failures not being caught by testing. I’ve already had two consumer products fail this year because of probable reliability issues: My MacBook Pro with 16GB of RAM started rebooting caused… Read More

DACis just 33 days away and who wouldn’t want a cool GoPro camerato play with? Your manager will certainly want you to first check out what’s new at DAC if your job involves getting to RTL signoff on time and within budget. The creative folks at Atrenta have figured out how to attract us with the offer of winning a GoPro camera,… Read More

ANSYS acquired Apache Design Automation back in June 2011and three years later the name “Apache” is being subdued in favor of using just ANSYS. One thing that I noticed right away was a DACfocus on having actual ANSYS customers talk about their hands-on experience using the EDA tools. The following seven customers… Read More

The big three in EDA are well-know for offering AMS and RF IC design flows, but today you also have alternative EDA vendors available that have capable tools, yet are lessor known. This blog will present an overview of the AMS and RF IC design flowoffered by Silvaco, an EDA company with a strong history in TCAD tools like Utmost IV for… Read More

Intel, Musk, and the Tweet That Launched a 1000 Ships on a Becalmed Sea