Eleven months ago I started a fitness kick in order to lose some weight, get healthy and have more energy, so I picked a familiar activity, road cycling. Being an engineer I have always loved measuring things, like my speed and distance, however I had an old-fashioned cyclocomputer called the Cateye Velo 2. This device connected … Read More

Author: Daniel Payne

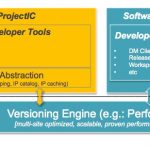

Speeding up IP and Data Management

IP and Data Management (DM) for SoC teams has gradually moved from ad-hoc approaches using simple Excel spreadsheets, to home-grown software that is specific to a project or company, and finally to commercially supported tools. One such commercial toolset for IP lifecycle management is from Methodics, named ProjectIC –… Read More

DAC Update on IC Design Tools at Mentor

On Tuesday morning I headed off to the Mentorbooth at DACfor an update on their Custom IC Design and AMS Simulation/Verification tools, Christopher Cone was the presenter. Also in the room were Jay Madiraju, and Mick from Berkeley DA.… Read More

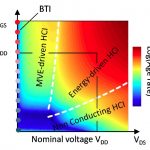

IO Design Optimization Flow for Reliability in 28nm

User group meetings are a rich source of information for IC designers because they have actual designers talking about how they used EDA tools in their methodology to achieve a goal. Engineers at STMicroelectronicspresented at a MunEDAUser Group on the topic: I/O Design Optimization Flow For Reliability In Advanced CMOS Nodes.… Read More

Making IP Reuse and SoC Integration Easier

The last graphics chip that I worked on at Intel was functionally simulated with only a tiny display size of 16×16 pixels, because that size allowed a complete regression test to be simulated overnight. Our team designed three major IP blocks: Display Processor, Graphics Processor and Bus Interface Unit. We wanted to also… Read More

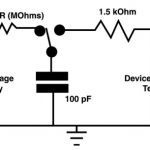

Ensuring ESD Integrity

Electro Static Discharge (ESD) is a fact of life for IC designs and has been ever since electronics were first created and then started failing because of sudden, large currents flowing through the design caused by human, processing or machine contact. It’s just too expensive to layout an IC today, fabricate it, test for … Read More

Power Modeling and Simulation of System Memory Subsystem

One great benefit of designing at the ESL level is the promise of power savings on the order of 40% to 70% compared to using an RTL approach. Since a typical SoC can contain a hierarchy of memory, this kind of power savings could be a critical factor in meeting PPA goals. To find out how an SoC designer could use such an ESL approach to power… Read More

Catching IC Manufacturing Defects With Slack-Based Transition Delay Testing

Test engineers are often the unsung heroes in the semiconductor world, because they have the tough job of deciding if each IC is good or bad, while taking the least amount of time on a tester and ensuring that the tests are actually finding and uncovering all manufacturing and process variation defects. Simple stuck-at fault models… Read More

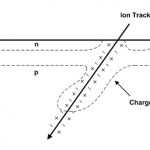

Modeling and Analysis of Single Event Effects (SEE)

Single Event Effects (SEE) are important because we depend upon our consumer, industrial and aerospace products to work reliably. Protons, electrons, neutrons, or alpha particles may perturb the MOS or bipolar device operation in either a destructive or non-destructive fashion. Galactic cosmic rays are one source of these… Read More

An Approach to Clock Domain Crossing for SoC Designs

Blogger Pawan Fangaria wrote about Clock Domain Crossing(CDC) a few weeks ago, and so I followed up tonight and watched a webinarabout CDC presented by Ravindra Anejaof Atrenta. An RTL design engineer would ultimately want a CDC verification tool that offers:

- Fast throughput and thoroughness

- Ability to debug and fix the source

Why Your LLM-Generated Testbench Compiles But Doesn’t Verify: The Verification Gap Problem