There’s no doubt that programmable logic in FPGAs have transformed our electronics industry for the better. If you do ASIC designs then there’s always the pressure of getting first silicon correct, with no functional or timing bugs, because bugs will cause expensive re-spins and delay time to market. ASIC designers… Read More

Author: Daniel Payne

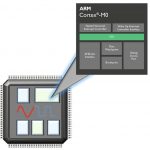

Securing Your IoT System using ARM

I’ll never forget reading about and experiencing the October 21, 2016 Distributed Denial of Service (DDoS) attacks which slowed and shut down a lot of the Internet. On that particular attack the target was to shut down the Domain Name System (DNS). Traffic for this massive DDoS attack came from IoT devices which were unsecured… Read More

Help for Automotive and Safety-critical Industries

I’ve been an Electrical Engineer and a car driver since 1978, so I’ve always been attracted to how the automotive industry designs cars to be safer for me and everyone else around the globe. According to statistics compiled by the CDCI learned that some 33,700 Americans died by motor vehicle crashes in 2014, which is… Read More

Something New for Semiconductor Parametric Testing

The familiar maxim that “time is money” certainly typifies our semiconductor industry where the mass production of chips, boards and systems helps to power our global economy and ever-increasing standard of living. The foundries that manufacture chips have to ensure that the process technology is in fact producing… Read More

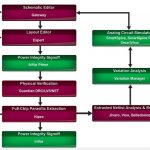

What You Don’t Know about Parasitic Extraction for IC Design

Out of college my first job was doing circuit design at the transistor-level with Intel, and to get accurate SPICE netlists for simulation we had to manually count the squares of parasitic interconnect for diffusion, poly-silicon and metal layers. Talk about a burden and chance for mistakes, I’m so thankful that EDA companies… Read More

Four Barriers to Using an SoC for IoT Projects

I often read about the large number of expected IoT design starts around the world, so I started to think about what the barriers are for launching this industry in order to meet the projections. One of my favorite IoT devices is the Garmin Edge 820, a computer for cyclists that has sensors for speed, cadence, power, heart rate, altitude… Read More

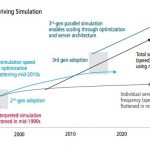

Making Functional Simulation Faster with a Parallel Approach

I’ll never forgot working at Intel on a team designing a graphics chip when we wanted to simulate to ensure proper functionality before tapeout, however because of the long run times it was decided to make a compromise to speed things up by reducing the size of the display window to just 32×32 pixels. Well, when first silicon… Read More

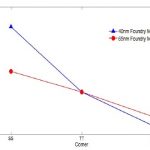

SPICE Model Generation using Machine Learning

AI and machine learning are two popular buzz words in the high-tech daily news, so you should be getting used to hearing about them by now. What I hadn’t realized was that EDA companies are starting to use machine learning techniques, and specifically targeted at the daunting and compute intensive task of creating SPICE models… Read More

Finding Transistor-level Defects Inside of Standard Cells

In the earliest days of IC design the engineering work was always done at the transistor-level, and then over time the abstraction level moved upward to gate-level, cell-level, RTL level, IP reuse, and high-level modeling abstractions. The higher levels of abstraction have allowed systems to be integrated into an SoC that can… Read More

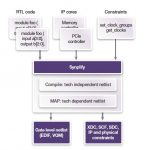

Four Steps for Logic Synthesis in FPGA Designs

I remember meeting Ken McElvain at Silicon Compilers for the first time back in the 1980’s, he was a gifted EDA tool developer that did a lot of coding including logic synthesis, a cycle-based simulator and ATPG. Mentor Graphics acquired Silicon Compilers with Ken included, and he continued to create another logic synthesis… Read More

Captain America: Can Elon Musk Save America’s Chip Manufacturing Industry?