Semiconductor companies are looking for ways to keep their business profitable by managing expenses on both the design and test side of electronic products, which is quite the challenge as the trends show increases in test pattern count and therefore test costs. Scan compression is a well-known technique first created over 15… Read More

Author: Daniel Payne

Understanding ISO 26262 Compliance for Automotive Suppliers

The semiconductor, IP, Software and EDA industries are all focusing on the growing automotive market because of its electronic content, size and growth. There are long-time suppliers to the automotive industry, and also first-time vendors that are launching something new every week for electronics in automotive. So where … Read More

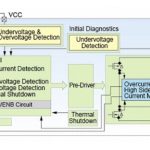

Electrothermal Analysis of an IC for Automotive Use

Automotive ICs have to operate in a very demanding environment in terms of both temperature and voltage ranges, along with the ability to withstand g-forces and be sealed from the elements. Not an easy design challenge. For many consumer ICs we see output drive currents on the IO pins measured in mA, however in automotive if you want… Read More

Webinar on TFT and FPD Design

I knew that the acronym for TFT meant Thin Film Transistors, but I hadn’t heard that FPD stands for Flat Panel Detectors. It turns out the FPD are solid-state sensors used in x-ray applications, similar in operation to image sensors for digital photography and video. I’ll be attending and blogging about what I learn… Read More

Achieving Requirements Traceability from Concept through Design and Test

Excel is a wonderful, general purpose spreadsheet tool that lets me organize and analyze rows and columns of data into something meaningful, however it doesn’t know anything about requirements traceability for complex semiconductor projects. So why do so many engineering teams still rely upon Excel or custom, in-house… Read More

Smart & Connected Devices to Artificial Intelligence and Beyond

Last Friday I attended a breakfast seminar organized by SEMI in Hillsboro, Oregon with fascinating speakers from several high-tech companies: Qorvo, Intel, Oregon Angel Fund, Kimera, Moonshadow Mobile and Yole Development. I recalled that Qorvo was created from the merger of TriQuint Semiconductor and RF Micro Devices back… Read More

An Overview of Jama Software in the Semiconductor Industry

Portland, Oregon is a hotbed of innovation for software development companies and I tend to scan the headlines of my local newspaper the Oregonian, which is where I first started to read about Jama Software a few years back. Curiosity and opportunity drove me to meet with Trevor Smith of Jama in their Portland office. We chatted for… Read More

IoT in the Cloud with Microsoft and Mentor

I cycle for fitness five days per week and use the Strava.com site to post my rides, analyze the ride data and chat with other cyclists, however in February this year the Amazon Web Services went down which crashed Strava, making me sad and nervous at the same time. Of course, there are alternatives to Amazon Web Services and the engineers… Read More

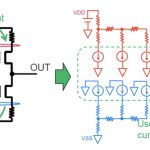

Approaches for EM, IR and Thermal Analysis of ICs

As an engineer I’ve learned how to trade off using various EDA tools based on the accuracy requirements and the time available to complete a project. EDA vendors have been offering software tools to help us with reliability concerns like EM, IR drop and thermal analysis for several years now. Last week I attended a webinar … Read More

Attending DAC in Austin for Free

I’ve been attending DAC since the late 1980’s and can tell you that it’s an annual highlight for me and anyone else interested in the EDA, IP and semiconductor industries. Where else can you see most of the big and little vendors of EDA software, semiconductor IP and foundries in one place? I recently blogged about… Read More

Captain America: Can Elon Musk Save America’s Chip Manufacturing Industry?