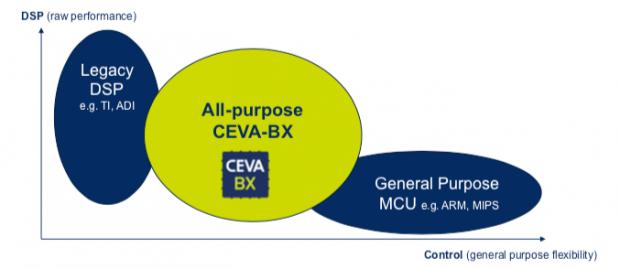

I’ve noticed hybrid solutions popping up recently (I’m reminded of NXP’s crossover MCU released in 2017). These are generally a fairly clear indicator that market needs are shifting; what once could be solved with an application processor or controller or DSP or whatever, now needs two (or more) of these. In performance/power/price-sensitive… Read More

Author: Bernard Murphy

Disturbances in the AI Force

In the normal evolution of specialized hardware IP functions, initial implementations start in academic research or R&D in big semiconductor companies, motivating new ventures specializing in functions of that type, who then either build critical mass to make it as a chip or IP supplier (such as Mobileye – intially)… Read More

Ampere: More on Arm-Based Servers

Since I talked recently about AWS adding access to Arm-based server instances in their cloud offering, I thought it would be interesting to look further into other Arm-based server solutions. I had a meeting with Ampere Computing at Arm TechCon. They offer server devices and are worth closer examination as a player in this game.… Read More

Big Data Analytics in Early Power Planning

ANSYS recently hosted a webinar talking about how they used the big-data analytics available in RedHawk-SC to do early power grid planning with static analytics, providing better coverage than would have been possible through pure simulation-based approaches. The paradox here is that late-stage analysis of voltage drops … Read More

ARM Answers Server Doubts

At ARM TechCon this year, the company announced the Neoverse brand targeted to infrastructure, contrasting with the Cortex brand we are familiar with for edge devices such as smartphones and IoT devices. Cortex was already used in infrastructure, in networking, base stations and the like but Neoverse splits the infrastructure… Read More

Imperas and RISC-V

I met Imperas at TechCon this year because I wanted to become a bit more knowledgeable about virtual modeling. That led me to become more interested in RISC-V and a talk given by Krste Asanovic of UCB and SiFive. My takeaway surprised me. I had thought this was an open-source David versus proprietary Goliaths (Intel and ARM) battle… Read More

Webinar: Turnkey Bluetooth True Wireless Stereo Earbuds and Speakers

When we were first introduced to earbuds, in-ear speakers connected through thin wires to your phone (and earlier portable music devices), they seemed pretty convenient for private entertainment at work, while walking, exercising, doing almost anything. Until we started to realize those long dangly wires weren’t ideal. They’d… Read More

Security and RISC-V

One of the challenges in the RISC-V bid for world domination may be security. That may seem like a silly statement, given that security weaknesses are invariably a function of implementation and RISC-V doesn’t define implementation, only the instruction-set architecture (ISA). But bear with me. RISC-V success depends heavily… Read More

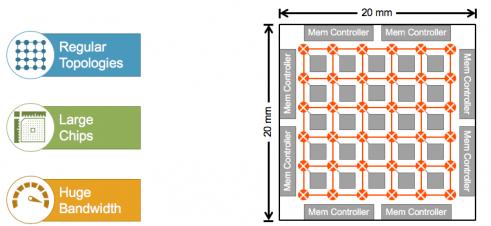

On-Chip Networks at the Bleeding Edge of ML

I wrote a while back about some of the more exotic architectures for machine learning (ML), especially for neural net (NN) training in the data center but also in some edge applications. In less hairy applications, we’re used to seeing CPU-based NNs at the low end, GPUs most commonly (and most widely known) in data centers as the workhorse… Read More

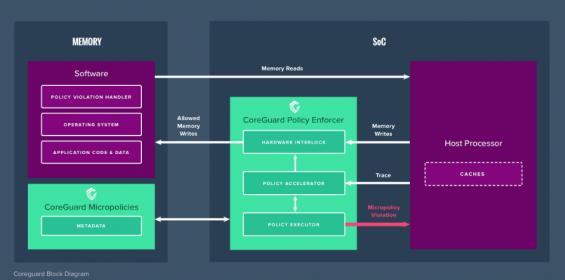

Dover Microsystems Spins New Approach to Security

One of the companies I met at ARM TechCon was Dover Microsystems who offer a product in embedded security. You might ask why we need yet another security solution. Surely we’re overloaded with security options from ARM and many others in the forms of TEEs, secure boots, secure enclaves and so on? Why do we need more? Because defending… Read More

Flynn Was Right: How a 2003 Warning Foretold Today’s Architectural Pivot