“Testing can only prove the presence of bugs, not their absence,” stated the famous computer scientist Edsger Dijkstra. That notion rings true to the many college participants of the Hack@DAC competition offered during DAC 2018 in San Francisco. The goal of this competition is to develop tools and methods for identifying security… Read More

Author: Alex Tan

Verification Importance in Academia

Keeping Pace With 5nm Heartbeat

A Phase-Locked Loop (PLL) gives design a heartbeat. Despite its minute footprint, it has many purposes such as being part of the clock generation circuits, on-chip digital temperature sensor, process control monitoring in the scribe-line or as baseline circuitry to facilitate an effective measurement of the design’s power… Read More

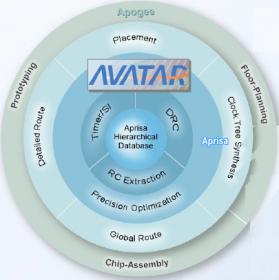

Aprisa and Apogee – The New Avatars

Earlier physical optimization impacts a design QoR gain and can disclose potential hurdles in dealing with unknown design variants such as new IP inclusion or new process node issues. Along the RTL-to-GDS2 implementation continuum, a left-shift move requires a robust modeling and proper context captures in order to produce… Read More

Accelerated Verification with Synopsys

At DAC 2018, Synopsys held a lunch panel discussing verification challenges faced by the industry leaders, their adopted approaches and the overall verification technology trends. This panel of industry experts from Intel, AMD, Samsung, STM and Qualcomm also shared their viewpoints on what drives the SoC complexity and how… Read More

Mentor Calibre Panel

Getting your tape-out done on time is hard, but can it be made easier? That was the main topic of Mentor’s Calibre Panel held at DAC 2018, attended by a few key players in IC design ecosystem: Bob Stear, VP of Marketing at Samsung represented the foundry side; from the IP side, Prasad Subramaniam, VP of eSilicon for R&D and Technology;… Read More

Liberate Trio Embraces ML and Cloud

A chain is as strong as its weakest link. This phrase resonates well in Static Timing Analysis (STA) domain, though it is about accuracy rather than durability. As timing signoff step provides the final performance readings of a design, an STA outcome is as good as its underlying components. Aside from the parasitic extraction … Read More

DAC 2018 Potpourri

The venue

Despite of being held at the new three-story Moscone West building, this year 55th DAC in San Francisco bore many similarities as compared with last year’s. Similar booth decors and floorplan positioning of the big two, Synopsys and Cadence, which were across of each other and right next to the first floor entrance –although… Read More

Achieving Clean Design Early with Calibre-RTD

Functional and physical verification are easily the two long poles in most IC product developments. During a design implementation cycle, design teams tend to push physical verification (PV) step towards the end as it is a time consuming process and requires significant manual interventions.

PV Challenges

In the traditional… Read More

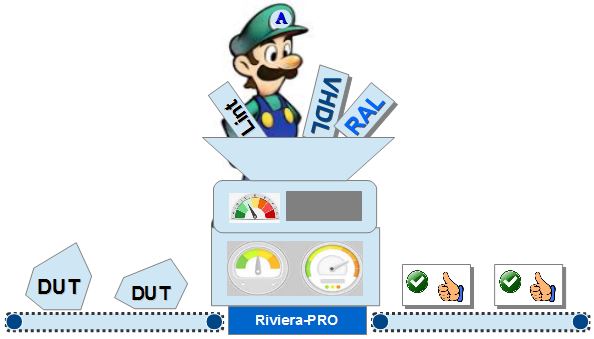

RAL, Lint and VHDL-2018

Functional verification is a very effort intensive and heuristic process which aims at confirming that system functionalities are meeting the given specifications. While pushing cycle-time improvement on the back-end part of this process is closely tied to the compute-box selection (CPU speed, memory capacity, parallelism… Read More

Managing Your Ballooning Network Storage

As companies scale by adding more engineers, there is a tendency to spread across multiple design sites as they strive to hire the best available talent. Multi-site development also impacts startups as they try to minimize their burn rate by having an offsite design center such as India, China or Vietnam.

Both the IoT and automotive… Read More

Things From Intel 10K That Make You Go …. Hmmmm