I’ve been working with AMIQ EDA for several years, and have frequently been impressed by new capabilities in their Design and Verification Tools Integrated Development Environment (DVT IDE) family. They just announced AI Assistant, which leverages large language model (LLM) technology. LLMs are much in the news these days,… Read More

The RISC-V and Open-Source Functional Verification ChallengeMost of the RISC-V action at the end…Read More

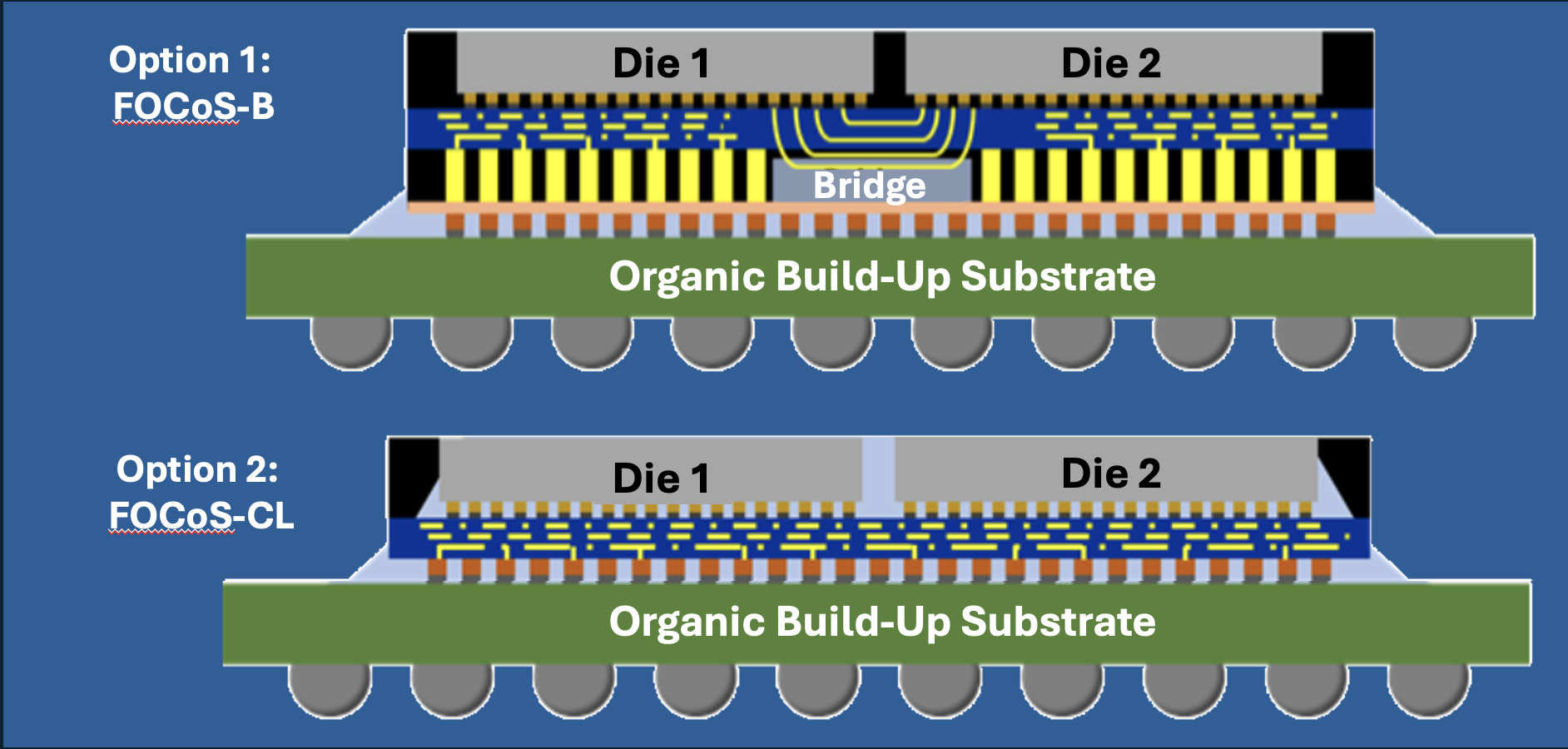

The RISC-V and Open-Source Functional Verification ChallengeMost of the RISC-V action at the end…Read More Sarcina Democratizes 2.5D Package Design with Bump Pitch Transformers2.5D package design is rapidly finding its stride…Read More

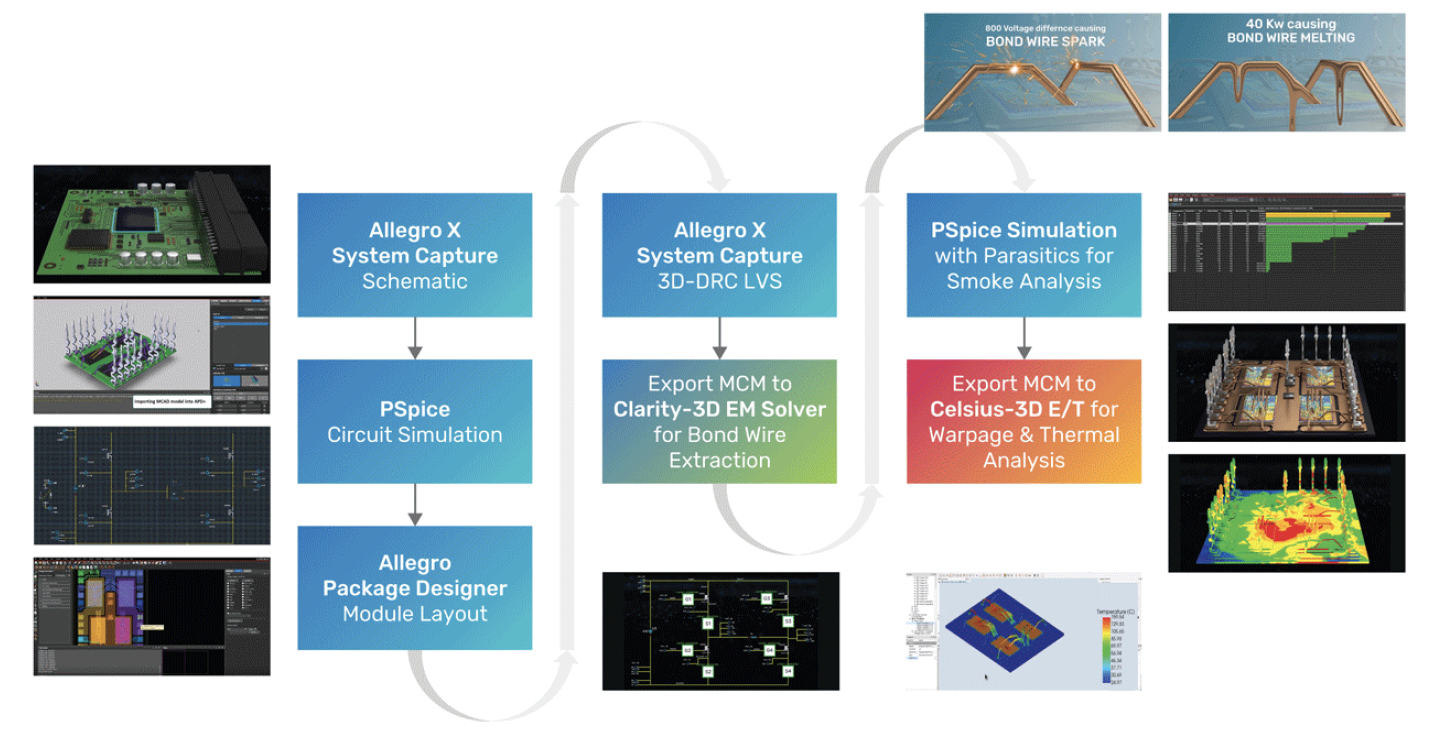

Sarcina Democratizes 2.5D Package Design with Bump Pitch Transformers2.5D package design is rapidly finding its stride…Read More Addressing Reliability and Safety of Power Modules for Electric VehiclesAs electric vehicles (EVs) gain widespread adoption, safety,…Read More

Addressing Reliability and Safety of Power Modules for Electric VehiclesAs electric vehicles (EVs) gain widespread adoption, safety,…Read More Shaping Tomorrow’s Semiconductor Technology IEDM 2024Anyone who has read my articles about IEDM…Read More

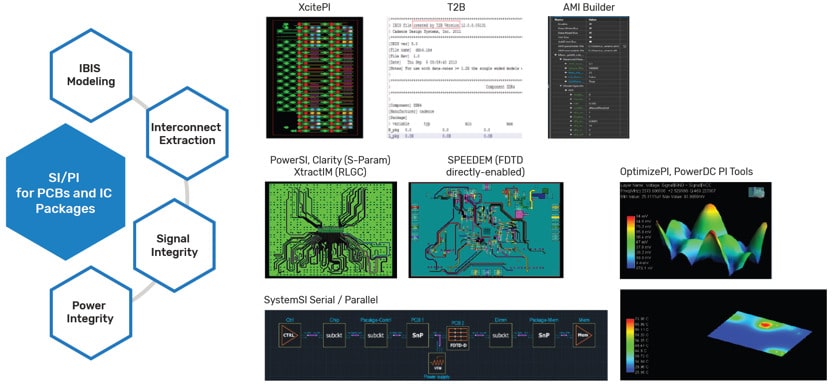

Shaping Tomorrow’s Semiconductor Technology IEDM 2024Anyone who has read my articles about IEDM…Read More SI and PI Update from Cadence on Sigrity XSignal Integrity (SI) and Power Integrity (PI) issues…Read More

SI and PI Update from Cadence on Sigrity XSignal Integrity (SI) and Power Integrity (PI) issues…Read MorePQShield Demystifies Post-Quantum Cryptography with Leadership Lounge

Post-Quantum Cryptography, or PQC provides a technical approach to protect encrypted data and connections when quantum computers can cost-effectively defeat current approaches. Exactly when this will occur is open to much discussion, but the fact is this day is coming, some say in ten years. One of the imperatives is to deploy… Read More

Datacenter Chipmaker Achieves Power Reduction With proteanTecs AVS Pro

As semiconductor technology advances and nodes continue to shrink, designers are faced with increasing challenges related to device complexity, power consumption, and reliability. The delicate balance between high performance, low power usage, and long-term reliability is more critical than ever. This growing demand … Read More

The Next LLM Architecture? Innovation in Verification

LLMs have amazing capabilities but inference run times grow rapidly with the size of the input (prompt) sequence, a significant weakness for some applications in engineering. State space models (SSMs) aim to correct this weakness. Paul Cunningham (GM, Verification at Cadence), Raúl Camposano (Silicon Catalyst, entrepreneur,… Read More

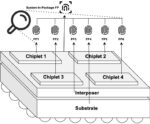

Defect-Pattern Leveraged Inherent Fingerprinting of Advanced IC Package with TRI

In the quest to secure the authenticity and ownership of advanced integrated circuit (IC) packages, a novel approach has been introduced in this paper that capitalizes on the inherent physical discrepancies within these components. This method, distinct from traditional strategies like physical unclonable functions (PUFs)… Read More

Podcast EP256: How NoC Tiling Capability is Changing the Game for AI Development with Andy Nightingale

Dan is joined by Andy Nightingale, VP of product management and marketing at Arteris. Andy has over 37 years of experience in the high-tech industry, including 23 years in various engineering and product management positions at Arm.

Dan explores with Andy the significance of the recently announced tiling capabilities and extended… Read More

How to Update Your FPGA Devices with Questa

It’s a fact of life that technology marches on. Older process nodes get replaced by newer ones. As a result, ASSPs and FPGAs are obsoleted, leaving behind large system design investments that need to re-done. Since many of these obsolete designs are performing well in the target application, this re-do task can be particularly … Read More

Overcoming obstacles with mixed-signal and analog design integration

Mixed-signal and analog design are key aspects of modern electronics. Every chip incorporates some form of analog IP, as even digital logic is dependent on analog signals for critical functions. Many digital design engineers are known to be uncomfortable with the prospect of integrating analog components. However, the current… Read More

Emerging Growth Opportunity for Women in AI

I was invited to the Fem.AI conference in Menlo Park, the first sponsored by the Cadence Giving Foundation with a goal to promote increased participation of women in the tech sector, especially in AI. Not just for equity, also to grow the number of people entering the tech/AI workforce. There are countless surveys showing that demand… Read More

LRCX- Coulda been worse but wasn’t so relief rally- Flattish is better than down

- Lam put in good quarter with flattish guide- still a slow recovery

- This is better than worst case fears of order drop like ASML

- China spend is slowing but tech spending increase offsets

- Relief rally as the market was braced for bad news and got OK news

Lam has OK, slightly better than in line quarter with OK guide….

It coulda been… Read More

AI Semiconductor Market