Last week, Synopsys announced an expansion of their Hardware-Assisted Verification (HAV) portfolio to accelerate semiconductor design innovations. These advancements are designed to meet the increasing demands of semiconductor complexity, enabling faster and more efficient verification across software and hardware domains.

At the pre-launch event, an insightful fireside chat took place between Ravi Subramanian, chief product management officer, Synopsys and Salil Raje, senior vice present and general manager, Adaptive and Embedded Computing Group at AMD. As they were not seated next to a fireplace, Ravi jokingly commented that fire is on at a fireplace somewhere. Having listened to this chat session and talks from Nvidia’s Narendra Konda, vice president, hardware Engineering and Arm’s Kevork Kechichian, executive vice present, Solutions Engineering, I’d say Synopsys is on fire and firing on all cylinders. AMD, Arm and Nvidia are a few among a much longer list of top tier customers who have already used the products that were announced last week.

The features, functionalities and specifications of the announced products are one thing to review. What is even more interesting is understanding why would top tier customers – who were given early access well before the launch – opt to run their key projects on these new solutions. What customer challenges are being addressed by the newly announced products from Synopsys. To uncover that, I chatted with Synopsys’ Tom De Schutter, SVP of Product Management and System Solutions and Frank Schirrmeister, Executive Director, Product Management and Systems Solutions.

Compounding Complexities Drive Advances in HAV

The rapid evolution of semiconductor technology is driven by four compounding complexities: software, hardware, interface, and architecture. As modern chips integrate billions of transistors, support heterogeneous computing, and execute increasingly software-defined workloads, ensuring their functionality has never been more challenging.

Software Complexity: Modern systems run sophisticated software stacks, requiring early software validation alongside hardware verification. HAV platforms enable pre-silicon software bring-up using emulation and FPGA-based prototyping.

Hardware Complexity: As chip architectures scale with more cores, accelerators, and advanced power management techniques, HAV provides critical functional verification and debugging to catch hardware flaws early.

Interface Complexity: Next-generation devices rely on high-speed interconnects (PCIe, DDR, Ethernet, UCIe, etc). HAV platforms help validate these interfaces under real-world conditions before silicon is produced.

Architectural Complexity: Workload-specific optimizations in AI, automotive, and cloud computing require extensive architectural validation. HAV allows engineers to analyze performance, debug bottlenecks, and refine power efficiency.

The interplay of software, hardware, interface, and architectural complexity makes HAV not just beneficial, but essential. Companies that fail to account for this compounding effect risk costly post-silicon bugs, longer time-to-market, and performance inefficiencies. HAV solutions provide a scalable way to tackle these challenges, ensuring robust and efficient semiconductor designs.

Verification happens in multiple phases, both pre-silicon and post-silicon, to ensure that designs function correctly before and after fabrication. With semiconductor innovations pushing boundaries, HAV ensures functional correctness, accelerates software development, and enables real-world validation, making it an essential pillar in modern chip design, amid growing complexities.

The Four Key Highlights of the Announcement

Synopsys’ HAV portfolio expansion strengthens the ability to manage hardware/software co-design, ensuring faster, more efficient integration and validation of complex systems in industries that depend on high-performance, real-time software.

Next-Generation Hardware Engines

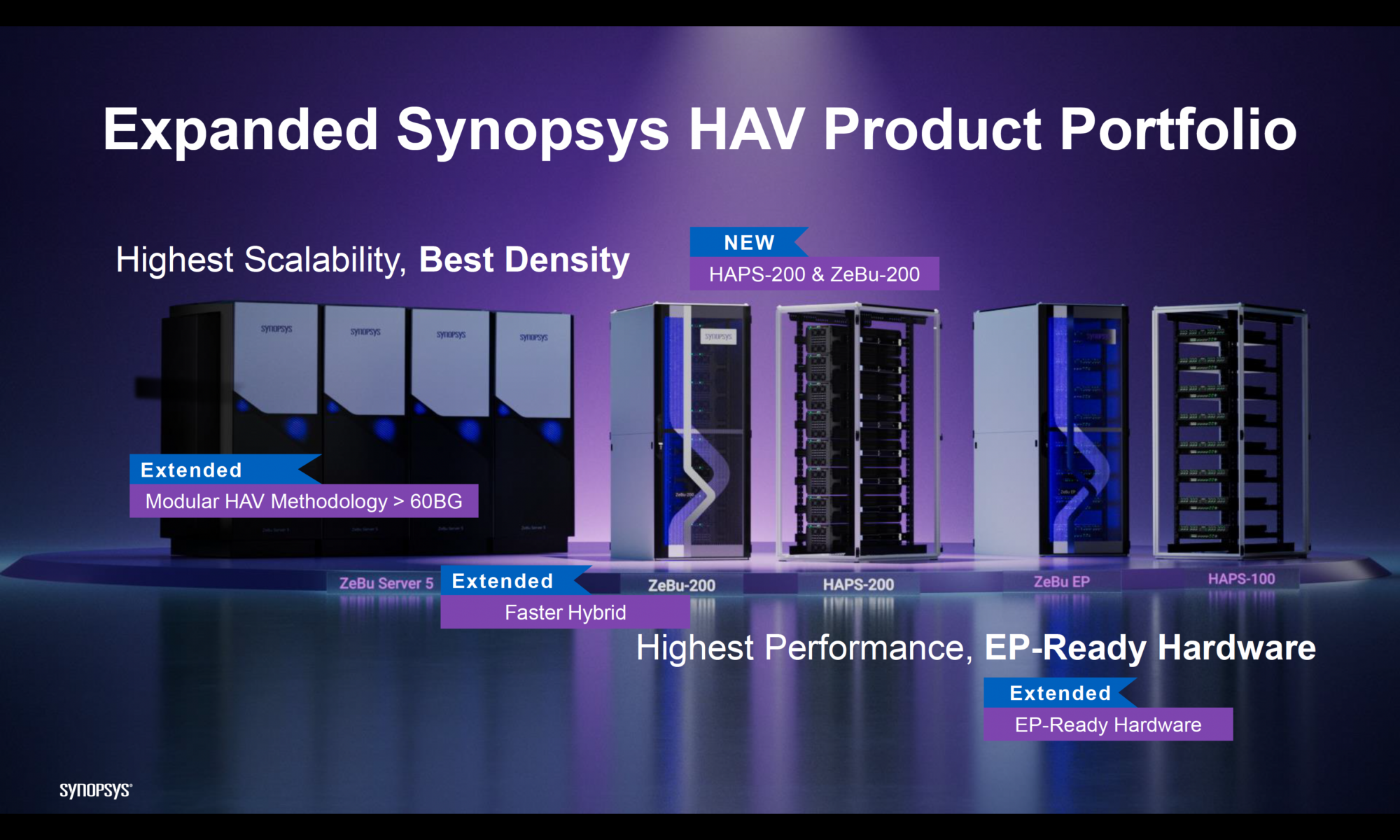

Synopsys has introduced ZeBu-200 for emulation and HAPS-200 for prototyping, delivering the fastest performance in the industry to significantly accelerate verification speed and efficiency. These next-generation hardware engines enable faster debug cycles, higher throughput, and improved system validation, making them essential for today’s complex semiconductor designs.

The HAPS-200 system delivers up to twice the performance and quadruples the debug bandwidth compared to its predecessor, the HAPS-100. It supports configurations ranging from single FPGA setups to multi-rack systems, accommodating designs up to 10.8 billion gates.

The Zebu-200 system delivers up to twice the performance and up to 8X better debug bandwidth compared to its predecessor, the Zebu-EP. It can accommodate designs up to 15.4 billion gates.

EP-Ready Expansion for Flexibility

Building on the success of the ZeBu-EP platform, Synopsys has now expanded EP-Ready configurability to both ZeBu (emulation) and HAPS (prototyping) platforms. This enhanced flexibility allows users to dynamically configure compute and connectivity resources, optimizing their investment across different verification workflows while seamlessly transitioning between emulation and prototyping.

Scalability for Massive Designs

With the extension of Modular HAV methodology to ZeBu Server 5, Synopsys now supports designs exceeding 60 billion gates, addressing the verification needs of next-generation, ultra-large semiconductor architectures. This expanded capacity enables efficient pre-silicon validation of complex chips, including multi-die and high-performance computing (HPC) systems, ensuring faster time-to-market.

Virtualization for Automotive and System Software

By combining virtual models running on a host server connected to a HAV system, software bring-up processes can be accelerated. Synopsys has integrated its HAV portfolio with Synopsys Virtualizer, creating this hybrid verification environment. This approach is especially critical for automotive software, where real-time system validation and high-performance execution are essential. By leveraging virtualization, engineers can develop, test, and optimize system software earlier in the design cycle, reducing risks and accelerating deployment.

EP-Ready Hardware Platforms, A Key Differentiator

EP-Ready stands for Emulation-Prototyping-Ready and is a key differentiator in Synopsys’ latest HAV portfolio expansion. The EP-Ready Hardware serves as the base module for compute and connectivity cabling for both prototyping and emulation. Initially introduced with the ZeBu-EP platform in 2022, this flexibility and configurability received strong positive feedback from customers. Now, Synopsys has extended EP-Ready Hardware capabilities to both HAPS-200 (prototyping) and ZeBu-200 (emulation) platforms, allowing users to seamlessly configure their verification environment based on workload needs. This unified approach optimizes performance, scalability, and return on investment (ROI) by providing a streamlined hardware foundation for multiple verification use cases. Customers do not have to decide on the balance of emulation and prototyping hardware upfront.

Summary

Synopsys has announced a significant expansion of its Hardware-Assisted Verification (HAV) portfolio, introducing new solutions to accelerate chip development and system validation. By expanding its HAV portfolio, the company continues to lead the way in high-performance verification, empowering semiconductor designers with scalable, configurable, and software-enabled solutions to drive next-generation chip innovation.

Video: Unveiling Next-Gen HAPS Prototyping & ZeBu Emulation Hardware-Assisted Verification Solutions

For more information and to access HAPS-200 and Zebu-200 spec sheets, visit the emulation and prototyping solutions page here.

For comprehensive Systems Verification and Validation solutions, visit here.

Also Read:

How Synopsys Enables Gen AI on the Edge

Will 50% of New High Performance Computing (HPC) Chip Designs be Multi-Die in 2025?

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.