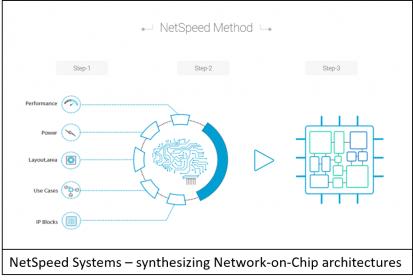

NetSpeed Systems is known for their network-on-chip (NoC) IP that enables complex heterogeneous SoC architectures. NetSpeed IP supports both non-coherent and coherent memory and I/O schemes as well as configurable, customized last level cache optimization through their Orion, Gemini and Pegasus IP respectively. They are also known for their NoCStudio software which uses artificial intelligence (AI) techniques to synthesize and analyze a NoC based on different security, power, performance, area and quality of service (QoS) requirements.

NetSpeed Systems is known for their network-on-chip (NoC) IP that enables complex heterogeneous SoC architectures. NetSpeed IP supports both non-coherent and coherent memory and I/O schemes as well as configurable, customized last level cache optimization through their Orion, Gemini and Pegasus IP respectively. They are also known for their NoCStudio software which uses artificial intelligence (AI) techniques to synthesize and analyze a NoC based on different security, power, performance, area and quality of service (QoS) requirements.

NoCStudio works exceptionally well, assuming you have good estimations of the types of network traffic that will be seen between various master-slave combinations of the SoC. The better the understanding of the expected network traffic, the better job NoCStudio can do to come up with an optimized NoC solution for your SoC. Depending on the end application however, this can be more complex than it first sounds. Obviously, designers can simulate the system but keeping track of the myriad of interactions going on between master-slave combinations while accounting for factors such as dynamically changing traffic profiles and varying workloads is not trivial. This approach requires greater insight into the interactions among the various subsystems and components on the chip itself.

NetSpeed addressed this challenge by announcing that they have teamed up with UltraSoC, a technology startup based in Cambridge, UK that specializes in embedded analytics IP. UtraSoC and NetSpeed have integrated UltraSoC’s monitors, debug ports, and analytical reporting to work seamlessly with NetSpeed’s IP and NoCStudio software. UltraSoC’s IP lets designers intelligently monitor and control the activity of on-chip structures such as custom logic, buses and CPU cores. This data can be used to better understand the system interactions within the SoC, revealing hard-to-find bugs, increasing quality and removing development risks and potential liability costs.

NetSpeed addressed this challenge by announcing that they have teamed up with UltraSoC, a technology startup based in Cambridge, UK that specializes in embedded analytics IP. UtraSoC and NetSpeed have integrated UltraSoC’s monitors, debug ports, and analytical reporting to work seamlessly with NetSpeed’s IP and NoCStudio software. UltraSoC’s IP lets designers intelligently monitor and control the activity of on-chip structures such as custom logic, buses and CPU cores. This data can be used to better understand the system interactions within the SoC, revealing hard-to-find bugs, increasing quality and removing development risks and potential liability costs.

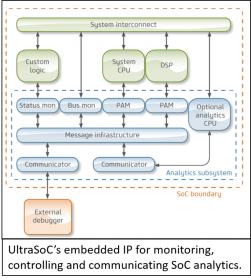

UltraSoC’s IP is modular, hierarchical and scalable and consists of three classes of IP. The first being made up of analytic modules that enable monitoring and control of system components. The second being a dedicated messaging infrastructure fabric that connects all the UltraSoC components. The third being a communicators interface module that connects the UltraSoC system to on-chip or external systems. Because UltraSoC’s IP is modular and scalable, it is an exceptionally good fit with NoCStudio as it has the degrees of freedom required to allow NoCStudio’s synthesis engine to be able to make the necessary system level trade-offs.

A key feature of the joint solution is that the UltraSoC IP provides the SoC designers with an unprecedented capability to help designers with post-silicon validation and debug of the SoC when it is first coming off the manufacturing line. The IP gives the engineers the ability to get a much better insight into how the system and NoC is really behaving when running the SoC for the first time. Designers can monitor a plethora of different traffic patterns through the system and get real time data on system performance by having the embedded monitors reporting data through the communicators module to either embedded software or to the outside world through different types of interfaces.

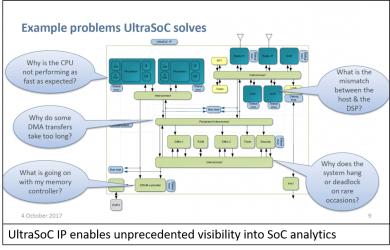

While the partnering companies are not necessarily advertising the capability, you’ve got to wonder how long it will be before a clever designer uses the joint solution to parameterize the NoC and system at design time and then use the embedded monitors and analytics to configure the system at run time through the UltraSoC messaging infrastructure. Imagine a system that can be monitoring itself using the analytic data and then adjusting its NoC setup to achieve software defined requirements based upon the application being handled by the SoC. Embedded software could be monitoring the SoC’s performance for things such as how long it is taking to make DMA transfers, or looking for mismatches between processors and dedicated hardware accelerators during certain compute intensive tasks and then take action to temporarily optimize the network traffic paths, all the while ensuring that QoS of other paths is being maintained.

While the partnering companies are not necessarily advertising the capability, you’ve got to wonder how long it will be before a clever designer uses the joint solution to parameterize the NoC and system at design time and then use the embedded monitors and analytics to configure the system at run time through the UltraSoC messaging infrastructure. Imagine a system that can be monitoring itself using the analytic data and then adjusting its NoC setup to achieve software defined requirements based upon the application being handled by the SoC. Embedded software could be monitoring the SoC’s performance for things such as how long it is taking to make DMA transfers, or looking for mismatches between processors and dedicated hardware accelerators during certain compute intensive tasks and then take action to temporarily optimize the network traffic paths, all the while ensuring that QoS of other paths is being maintained.

Combining UltraSoC’s IP with NetSpeed Systems’ NoCStudio and NoC IP is a very complimentary and smart connection. It enables the SoC designers to embed structures that will enable them to more quickly bring-up the SoC and then integrate the chip into various systems by looking at data from the chip itself. And, as eluded to earlier, the system has legs to enable some truly unique capabilities in the future for software defined NoCs (SDNoCs). While UltraSoC’s IP is scalable and parameterized, what better way to make use of those features than to have NoCStudio’s synthesis engines use them during its trade-offs. Add the capability to synthesize in flexibility based on embedded system monitors and you’ve got a system that can literally tune itself to its work load. Very impressive.

Combining UltraSoC’s IP with NetSpeed Systems’ NoCStudio and NoC IP is a very complimentary and smart connection. It enables the SoC designers to embed structures that will enable them to more quickly bring-up the SoC and then integrate the chip into various systems by looking at data from the chip itself. And, as eluded to earlier, the system has legs to enable some truly unique capabilities in the future for software defined NoCs (SDNoCs). While UltraSoC’s IP is scalable and parameterized, what better way to make use of those features than to have NoCStudio’s synthesis engines use them during its trade-offs. Add the capability to synthesize in flexibility based on embedded system monitors and you’ve got a system that can literally tune itself to its work load. Very impressive.

If you want to find out more about this new approach, NetSpeed Systems and UltraSoC will be hosting a joint webinar to discuss this solution in more detail. The webinar entitled: Debug, Analytics, NoC, and beyond… Exploring uncharted galaxies of interconnects!Will take place on November 2, at 17:00 GMT (UK time). To see more details of the webinar and to register for the event use this link.

See also:

NetSpeed Systems offerings

UltraSoC offerings

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center