In our previous article bearing the same title, we discussed the recommended baseline checks covering cell and pin presence, back-end, and some front-end checks related to functional equivalency. In this article, we’ll cover the extensive list of characterization checks, that include timing arcs, NLDM, CCS, ECSM/EM, and NLPM.

![]()

Timing Arc Checks

The recommended timing arc checks should include checking equivalence of WHEN and SDF conditions in a given liberty file, condition consistencies across different timing corners, and Liberty vs. Verilog/VHDL arc consistencies. This is essential in order to ensure accurate digital simulations and timing analysis.

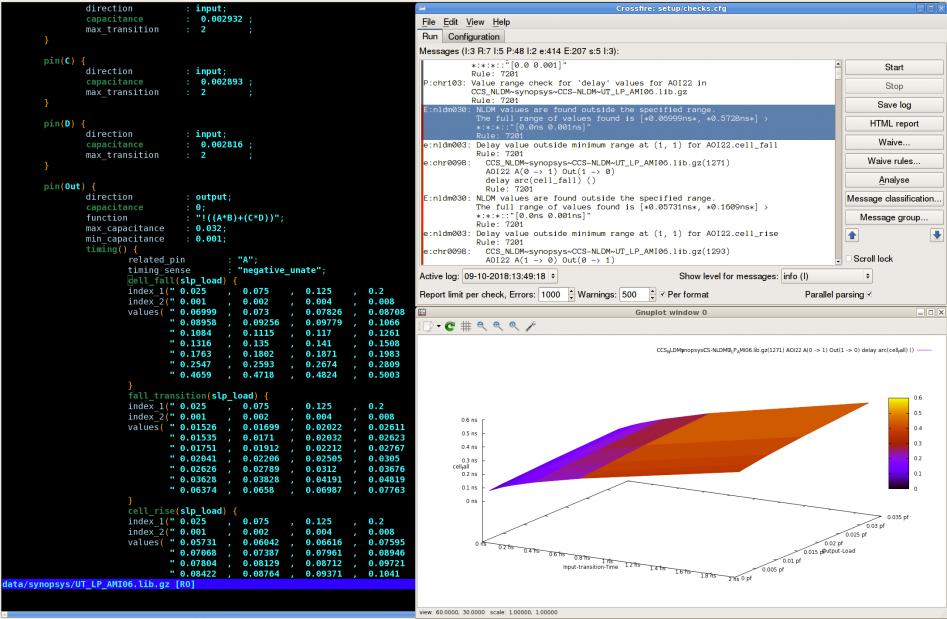

NLDM Characterization Checks

NLDM related characterization QA should include consistency checks between delay and transition tables, ascending capacitance and transition index values, correct number of indices, and range checks for delay, transition, setup/hold, and minimum period. Ensuring that cell rise and fall delay values don’t vary too much can be a valuable check for clocks, as well as other ports that may require a balanced delay.

It may also be prudent to ensure delays increase with increasing output capacitance, input transition times, and decreasing supply voltage. At the same time, checking that both transition and capacitance values don’t fall outside the range of the defined maximum transition and capacitance is also a necessity. This will ensure that no extrapolation is needed when characterized data is used in a design flow environment. In terms of transition trip points, one must ensure that they are symmetrical and must be a given percentage outside of the delay trip points. Other accuracy checks should include checking for non-changing or zero delay or transition values in a given table.

When comparing two or more PVT corners, large delay deviations should be closely monitored, exact values should not repeat, pin properties and parameters should be consistent, and mode definitions should match. Capacitance and transition properties should be consistently defined for all pins. More importantly, ensuring the same tables and arcs are defined across all given corners will provide a more stable and error-free timing analysis down the line.

Constraint values and related timing information such as setup and hold tables should be defined in matching pairs. Each matching setup and hold tables should have equal indices, and the sum of setup and hold values should be greater than zero. For clock related pins, ensuring pulse width definitions is also necessary.

Additional consistency checks should flag cases where duplicated or illegally defined parameters are used and ensure user-defined parameters are correct. Temperature, voltage, and process corner parameters should be consistent with the library and file name. On top of this, units must be consistent and defined as expected. Pin related checks should guarantee the presence of arcs and the use of required tables and omission of obsolete ones. An important, yet often overlooked check, should ensure that related pin terminals are not defined as outputs.

For standard cell libraries, cell to cell trends with respect to changes related to increasing output drive should be closely monitored. They include area, cell footprint, pin attributes, arc consistency, delay, and power monotonicity. Also, ensuring consistency among the attributes pertaining to power switch cells and its pins will guarantee correct usage of specific cells.

On-chip variation related timing checks should include table presence, monotonicity, and guarantee that all files are paired correctly (when comparing NLDM to AOCV/POCV files).

CCS Characterization Checks

CCS power characterization can also benefit from many of the above checks along with ensuring that all given templates follow the Liberty specification guidelines. The nominal voltage must match the operating condition voltage. This is essential is guaranteeing correct data for a given voltage corner. The dynamic current group must be present for all cells and for power pins, the current must be positive, and negative for ground pins. Additionally, the reference time must be greater than zero since it’s related to physical circuit behavior. The same checks also apply to leakage current. In the absence of gate leakage values, current conservation must hold within the same leakage current group. If all power and ground pins are specified with leakage currents, the sum of all currents should be zero. Finally, when dealing with intrinsic resistance, total capacitance, or intrinsic capacitance, values should not be negative or zero.

ECSM/EM Characterization Checks

Effective Current Source Model (ECSM) and Electro-Migration (EM) related checks are in line with those specified for CCS. Beside ensuring that all tables are consistent across all corners, current values must also be checked to ensure monotonicity across given capacitive loads. Checking for the presence of a given combination of average, peak, and RMS current types may be a design specific requirement that would need to be qualified as well.

NLPM Characterization Checks

Last, but not least, power related characterization checks should include the standard and expected trends related to capacitance, transition times, and voltage. Power is expected to increase when load capacitance or transition times increase. At the same time, it is expected to decrease when supply voltages decrease. In terms of leakage power, one might want to ensure that values fall within an expected range and check whether pins are correctly defined for a given condition, whether they are required or missing.

Conclusion

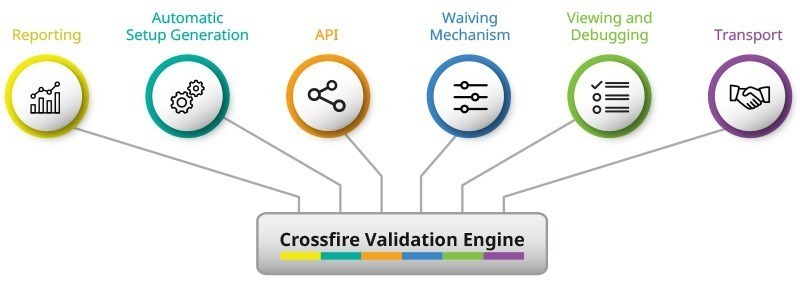

Although we have already mentioned this in the previous article, it is important to repeat it… IP qualification is an essential part of any IC design flow. A correct-by-construction approach is needed since fixing a few bugs close to tapeout is a recipe for disaster. Given that, IP designers need a dedicated partner for QA solutions that ensures the QA needs of the latest process nodes are always up-to-date. In-house QA expertise increases productivity when integrated with Fractal’s Crossfire validation tool. All framework, parsing, reporting, and performance optimization is handled by the software. On top of that, with a given list of recommended baseline checks, we ensure that all customers use the same minimum standard of IP validation for all designs.

Also Read: Crossfire Baseline Checks for Clean IP

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.