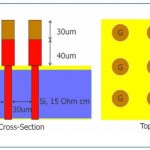

Twenty eight nanometer is progressing very well. Our output and our yields are both above the plans that we set for ourselves and the plans that we communicated to our customers early in the year. Early in the year means January-February of the year, we set our plans in output and in yields and we, of course, ever since then we tried to exceed the plan and we had also communicated the plan to our customers at the time. And we have indeed exceeded the planned in both output and yields.

We expect to ramp up to about 68,000 wafers per month by the end of the year, 28 nanometer, 68,000 12-inch wafers per month by the end of the year. And by fourth quarter, we will be nearly caught up with the demand and we expect to fully meet the demand from the first quarter of 2013 on we will fully meet the 28 nanometer demand. It is also then that we expect that the 28 nanometer gross margin will catch up with the corporate average.

As I said today, both the defect density and use are better than 40 nanometer at the same stage of the volume ramp and they are also better than what we have – what we planned early in the year and what we communicated to our customers at that time.

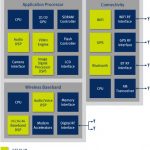

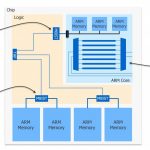

Now, next a few words on 20 nanometer, 20 SoC. We have made very good progress on the 112 megabit SRAM yield. Now there are still challenges to overcome in meeting our yield plan of the entire chip. We have made very good progress on 112 megabit SRAM, there are still challenges to overcome in meeting our yield plan of the entire chip, which has both the logic and the SRAM on that, of course.

Now, our 20 nanometer SoC, we believe, is fully competitive with industry leaders, other companies’ 22 nanometer for the served available markets that we serve. For our markets, we believe our 20 SoC is fully competitive with anyone’s 20 nanometer or 22 nanometer offering.And, one important point to make is that our 20 nanometer has the industry’s leading metal pitch of 64 nanometers. Our leading competitors have 80 nanometer metal pitch. That allows an advantage in the device’s density and die size.

Now, as for the timing, we expect our 20 nanometer technology to be qualified by the end of this year and will be ready to support customers (inaudible) in Q1 of 2013. I think that we’ll start some production of 20-nanometer next year, but the small scale, very, very low, what we would call risk type of production basically, but 2014 will be a ramp year for 20-SoC.

Now today, last time I mentioned that we will have a FinFET product after 20 SoC. And today, I’m glad to say that we have been planning the 16 nanometer FinFET. Right after our 20 nanometer (inaudible), which is the 20 SoC, we will offer FinFET at 16 nanometer for significant active power reduction. We expect to achieve speed and density, speed and logic density levels comparable to industry’s leading players 14 nanometer FinFET.

So, we expect our 20 SoC to be competitive with competitors’ 22 nanometer or 20 nanometer products and we expect our 16 nanometer FinFET to be competitive with our competitors’ 14 nanometer FinFET products. You might ask why are we calling it 16. The only reason, in fact, until two days ago, we were undecided on whether to call it 14 or 16 FinFET. Now the only reason we decided to call it 16 FinFET is first, we want to be somewhat modest; second, we are told quite a few major customers ask the 16 FinFET, that designation and we didn’t want to confuse our customers by now switching to 14. But we expect it to be competitive with other people’s 14 nanometer offerings.

Now 16 nanometer FinFET, our 16 nanometer FinFET, is expected to deliver about 25% speed gain given the same standby power over the 20 nanometer SoC. It is expected to give 25% to 30% power reduction at the same speed and the same standby power, and for mobile products, it is expected to give 10% to 20% speed gain at the same total power. As for timing, we expect it to be about one year after 20 SoC namely it should be ready for risk production at the end of 2013 or early 2014, about one year later than the 20 SoC.

Now, why are we having such high capital intensity? Now, well, I think this is actually a focus point of our internal discussion among our top level managers for the last two years now. And basically, we invest in capacity to get future growth. So you look back at history. If you look at our TSMC’s history, during ‘97 and ‘02, between 1997 and 2002, during that six-year period, TSMC’s capital intensity ratio stayed mostly above 60%, 60% during that six-year period. And then was, as you recall, there was a high-tech bubble bursting in late 2000 and early 2001. But in spite of that, our revenue CAGR between ‘97 and ‘07, here after having spending a lot of capital, having sustained high capital intensity for six years, ‘97 to ‘02, our revenue CAGR between ‘97 and ‘07, that’s a 10-year period, was 20%, compounded annual growth rate of 20% in revenue during the 10-year period; the first six of which was marked by high capital intensity. During that 1997 to 2007 period, foundry industry growth was 16% in the same period and ours was 20%. As a result, our market share rose from – foundry market share – from 31% in ‘97 to 43% in ‘07.

And as far as this year’s CapEx is concerned at this point, we are still following the guidance that we gave you last time; I believe NT$8 million to NT$8.5 million. At this point we are still following that. But next year, I am – we are not going to forecast until early next year. But I think I have already given you a view of our reasoning and our strategy and our objectives. So but as to the exact number, I will not give you until early next year.

13 page transcript is HERE.