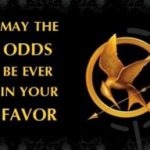

Risks and Rewards of Engaging with EDA Startups:The Hunger Games!

Doing business with EDA startups comes with both risks and rewards. The Hogan’s Heroes panel at DAC 2013 features key decision makers from fabless, startup and vc firms sharing candid opinions on this risk/reward equation, and the financial and technical issues of engaging with EDA startups.

·How often do companies “burn out” and users “get burned?”

·How can you protect yourself?

·And, how do customers sometimes contribute to the rise and fall?

Jim believes that startups are the innovation engine of EDA.“If you do not invest in small companies, you will get roadmaps from the EDA “gorillas” but not much new technology. Certainly there is risk, but without startups, we don’t see a lot of innovation.”

Hear what the panelists have to say!

Moderator: Jim Hogan, Private Investor

Jim is currently the managing partner of Vista Ventures, LLC. Jim has worked in the semiconductor design and manufacturing industry for more than 35 years gaining experience as a senior executive in electronic design automation, semiconductor intellectual property, semiconductor equipment, and fabrication companies. Mr. Hogan holds a B.A degree in mathematics, a B.S. degree in computer science and an M.B.A., all from San Jose State University.

Panelist: Atul Sharan, Artiman Ventures

Atul is currently Entrepreneur in Residence, Artiman Ventures. Previously, Investment Advisor at Darwin Venture Management; President & CEO AutoESL (acquired by Xilinx); Corporate Consultant at Cadence Design Systems; Founder, President & CEO at Clear Shape Technologies (acquired by Cadence); Resident at Mohr Davidow Ventures; Vice President – Marketing, Business Development & Applications at Synopsys; Senior VP – Worldwide Sales & Marketing at Numerical Technologies Inc. (IPO; acquired by Synopsys); Business Development & Marketing at Ambit Design Systems (acquired by Cadence); GM – India Operations at VLSI Technology Inc., Compass; Engineering Manager at Altera; and at IDT. Atul’s education spans the University of California, Berkeley – Walter A. Haas School of Business, MBA, Finance & Management; University of Houston MS, Engineering; and IIT Kanpur, BS, Engineering.

Panelist: Sanjay Lall, Board of Directors, Ausdia Inc.

Sanjay Lall is currently on the Board of Directors at Ausdia, with over 20 years of experience in the electronic design automation (EDA) and semiconductor industries. Sanjay is also chairman and managing partner at Cronox Group, on the board of advisors at Verdigris Technologies, and a director at Mobi-holdings.Previously VP of worldwide sales at Extreme DA, acquired by Synopsys in2011; President and CEO at Silicon Software; President & CEO at NION Interactive; and accelerated sales growth for EDA companies such as Sente (acquired by Frequency Technology), Triquest (acquired by Summit Design), Ultima Interconnect (acquired by Cadence), Frontline Design Automation (acquired by Avanti), CadMOS (acquired by Cadence), Plato Design (acquired by Cadence), Q Design (acquired by Cadence), Brion Technology (acquired by ASML) and Epic Design (acquired by Synopsys).He holds a B.S.in electrical engineering and computer science from Santa Clara University.

Panelist: Dave Crohn, Senior Director, Engineering, Broadcom….and DAC Party Singing Idol!

Dave currently manages all of EDA for Broadcom Corporation, a leader in the industry providing broadband communications. Dave had done design work for 24 years starting with Sperry (later Unisys) back in the ECL days; ETA Systems designing a 10 GFLOP supercomputer in liquid nitrogen; Siemens including 1 year working in Munich; ADC Telecommunications; then Motorola; and finally on to Broadcom where he’s been for the last 14 years. At Broadcom he originally managed the standard cell team and later moved into the managing EDA role at Broadcom for the last 9 years. Working for thedifferent companies gave Dave the opportunity to work with many different EDA tools as well as different technologies throughout his career. This now lends itself to working with engineering at Broadcom to determine best in class technology to pursue corporate-wide. Dave also negotiates the contracts and manages EDA supplier relationships. Dave holds a BSEE from the University of Minnesota.

Let the EDA Hunger Games Begin…

Join us Tuesday, June 4, at DAC 2013 in Austin Texas. For more information, please see www.dac.com

And, to EDA startups and their customers:

“May the odds be ever in your favor!

Ever in your favor…..”