It appears that immersion lithography is now the plan of record for manufacturing ICs at 14nm. How is it possible to use 193nm wavelength light at 14nm? How can we provide the process window to pattern the such tight pitches? The secret lies in computational lithography. For 20nm, the two key innovations in computational lithography involve enabling double patterning with concurrent OPC, and in improving difficult-to-print layouts with localized in-situ optimization and by using an inverse lithography technique.For 14nm, says Mentor Graphics’ OPC product marketing manager Gandharv Bhatara, computational lithography offers more tools for process window enhancement with better approaches to sub-resolution assist features (SRAFs). SRAFs have been used since the 130nm node for resolution enhancement, but for 14nm, SRAF placement has evolved considerably. In a recent article, Bhatara says that SRAF placement has moved from rules-based to model-based, and describes two new model-based approaches developed in the Mentor OPC tools. One approach uses inverse lithography (ILT) to create the golden reference for a rules-based SRAF placement. This gives superior process window for critical blocks like SRAM, where the rules are relatively easy to develop. The second approach is a true model-based approach, where a model is used to determine which areas on mask would benefit most from SRAFS and also to perform the initial SRAF placement. The model-based approach is particularly useful for random logic designs, where developing rules continues to be challenging. Both methods are good, but for different design styles. Bhatara says that for 14nm, combining them into a hybrid approach provides a single, unified SRAF recipe for SRAM (rules-based) and random logic designs (model-based). So if you need the keys to 14nm computational lithography, look for advanced SRAF solutions that provide flexibility, control runtime, and leverage both rules-based and model-based approaches.You can find this and other content on foundry-based IC design and manufacturing at www.mentor.com/solutions/foundry.

PCI Express IP vendor Cascade acquisition by Synopsys…

… is now 8 years old, and the money paid for this 10 engineers start-up was considered, at that time, as a “bingo” for Cascade’s funders: “In October 2004, the Company completed the acquisition of Cascade Semiconductor Solutions, Inc. (Cascade) for total upfront consideration of $15.8 million and contingent consideration of up to $10.0 million to be paid upon the achievement of certain performance milestones over the three years following the acquisition ” (this quote being extracted from the 10K form filled by Synopsys in 2005). Even if we don’t know if the $10 million have been paid or not, this deal was a pretty high valuation for a 10 engineers start-up, and their flagship product, the PCI Express (gen-1 at that time) Controller, supporting Root Port, EP, SW and Dual Mode configuration. I am sure that, at that time, some people were laughing about Synopsys and the money spent in this acquisition…

If we have a look at the cumulated revenue generated by PCI Express IP product line from 2005 to 2012, we have to keep in mind that most of these IP have been generated after this acquisition, so we can’t simply claim that this initial investment has returned X time the money, but it was clearly a “big bang” explosion ringing PCI Express IP market take off.

This long list of PCI Express Controller, PHY and Verification IP:

- Endpoint Configurable PCIe 3.0, 2.1 and 1.1 IP for Endpoint applications

- Root Port Configurable PCIe 3.0, 2.1 and 1.1 IP for Root Port applications

- Dual Mode Configurable PCIe 3.0, 2.1 and 1.1 IP for RC or EP applications

- Switch Port Configurable PCIe 3.0, 2.1 and 1.1 IP for Switch applications

- PCIe to AHB bridge Adds PCI Express external connectivity to AMBA 2.0 AHB-based SoCs

- PCIe to AXI bridge Adds PCI Express external connectivity to AMBA 3 and 4 AXI-based SoCs

- SR I/O Virtualization Configurable PCIe 3.0, 2.0 and 1.1 IP with SR-IOV support

- 1.1 PHY Low power, small area PCI Express 1.1 PHY operating at 2.5 Gbps

- 2.1 PHY High performance, low power PCI Express 2.1 PHY operating at 5.0 Gbps

- 3.0 PHY Multi-channel, low power PCI Express 3.0 PHY operating at 8.0 Gbps

- Verification IP Verifies PCI Express 3.0, 2.0 and 1.1 EP, Switch, and RC devices

Such a port-folio help understanding why Synopsys has generated $133.60 million between 2005 and 2012, or 8 times the money invested into Cascade, leading the company to get 62% market share of the PCIe IP segment last year!

PCIe as a technology is clearly here to stay, and we will certainly use in 2020, on a day to day basis, electronic systems relying on PCI Express in one way or another. If PCI Express technology was initially developed for applications like PC, Server, PC Peripherals or Communication, the technology penetration in Networking, Aerospace, Test Equipment, Imaging or Medical applications also explains Synopsys’ success during the last decade. Such a safe way to interconnect IC within the same system or between two completely different applications designed by two different teams, who even don’t know which system will be interconnected to their application, in fact the definition of a standard protocol, has no reason to disappear… except obsolescence. To escape obsolescence, a very good way is to keep defining more efficient and fastest version of the protocol: PCIe gen-2, running at 5 gbps and per lane came pretty soon after gen-1 (2.5 Gbps) definition, say in 2007. Now in 2013, PCIe gen-3 running at 8 Gbps is becoming the mainstream, and we can expect to see gen-4 to be defined soon, running at 16 Gbps!

The other way to avoid obsolescence is the pervasion in new segments, and the PCI-SIG has been pretty active recently, as they have defined three new standard extensions:

- M-PCIe: Mobile PCI Express will be used with MIPI M-PHY to interconnect IC in a mobile system, like media tablet or smartphone

- SATAe: SATA Express will replace SATA to access data stored in HDD, the above picture coming from SATAI/O

- NVMe: Non Volatile Memory Express will be used to access data stored in or Solid State Devices (SSD).

So, PCIe technology is here to stay, and the PCIe IP market has found new resources for growth. Now, we can say that the price paid for Cascade acquisition was a cleaver investment made by Synopsys… 8 years ago.

Eric Esteve from IPNEST

lang: en_US

FinFET Design Challenges Exposed!

The first mention of FinFETs appeared on SemiWiki after the ISSCC conference in 2011. Dr. Jack Sun, TSMC Vice President of R&D and Chief Technology Officer, spoke about the power crisis the semiconductor industry is facing and FinFETs was one of the promising technologies that could help us. Since then, we have posted 100+ related articles with FinFET being the top trending term for search engine traffic coming to SemiWiki in 2012. That is why Dr Chenming Hu, the father of FinFETs, is the covetedKaufman Award winner this year and why I agreed to keynote FinFET day at the EDPS Conference in Monterey this month. They should call them FunFETs because we are certainly having a good time!

Recently I was invited to an informal back yard BBQ with a group of layout people who are working on FinFET test chips. Layout people are a different breed for sure but you will not meet a harder working group in the semiconductor ecosystem, believe it. And FinFETs are not making their life any easier!

My mother was very analytical, a natural born engineer. Unfortunately, in the 1950’s women weren’t encouraged to work outside the home much less become engineers but she did anyway and ended up being a draftsperson working on the Apollo Space program. I remember getting the VIP treatment as a kid at her work place and noticing that the clear majority of her coworkers were women, except management of course.

It was deja vu all over again when I worked with layout groups in Silicon Valley in the early 1980’s. Mostly women, none of which had engineering degrees but, like my dear mother, were engineers at heart and very good at what they did. 30 years later quite a bit has changed with layout groups and tools given that the job is much more difficult with all of the design and manufacturing advances we have seen over the years.

One of the things that has NOT changed however is the Design Rule Manuals (DRMs). They are still the center of the layout universe, they are still in paper or PDF form, and they are a growing problem for layout people. Process technologies are coming at them faster every year. Design rules are much more complicated and change more frequently during the “maturing” period. DRMs are much more cryptic and tape out schedules are staying the same. Clearly DRMs are going to have to change if we are going to continue down this path otherwise schedules will slip, mistakes will be made, layout people will spontaneously combust, not a pretty picture believe me. Adding layout head count will not help either since it takes years to master leading edge layout. In fact that is what has saved us thus far, the depth of experience the average layout person has today.

The change that is coming, the change that has to come, is with the DRMs. As a communication tool between the foundries and the fabless semiconductor companies it is failing. We need to provide the information REQUIRED to efficiently and effectively layout modern semiconductor devices. What we need is an Interactive Design Rule Manual that brings design rules to life! Sound reasonable?

A Non Deterministic Timing Problem

When I was not messing around with FPGA Research and Development, or Algorithms, I was often called into the lab or field and presented this type of scenario… Most of the time, the fix was the same…

At least a few times a year, I’d get the call. Sometimes a panic in the voice, or sometimes defeat. And who wouldn’t be defeated? After all, the FPGA design worked in PowerPoint :p and in ModelSim. The designers scrubbed and polished all the timing warnings and it was go time, excitement was in the air. The bosses were happy as earned value was thru the roof and believed that this FPGA was only going to be routed once! Then the worst case scenario was happening. “A Non Deterministic Timing Problem”… The panic would get so bad that the engineers would start using the ‘R’ word ‘RANDOM’, I wanted to patent their RANDOM design and just retire, but then I recalled the company was paying me to solve this problem.

So standing usually in front of some VME chassis, I would start asking a series of questions, like who did your hair? No, seriously I use humor to diffuse the much stressed, tired, cranky managers and engineers. Sometimes it even worked. I would ask:

- After a power cycle or cold start what happens?

- Has this problem always presented this way, i.e. , software change (hey, got to blame the software guys…)

- How long into the ‘run’ before the problem occurs?

- Is it repeatable? What has changed?

- Was the top level simulated?

- How many clock domains does the FPGA have?

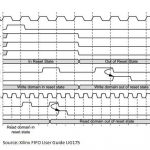

- Did you use Asynchronous FIFOs to cross those domains and use either an EMPTY FLAG or the like to push/pull data?

Believe it or not, those two last questions have solved most of the hard FPGA system integration type questions over my career. It was sometimes due to a fancy or green FPGA designer thinking he could design around the clock boundaries and not use asynchronous FIFOs. Other times it was the assumption on data rates. The designer thought that the FIFO would never go empty so why look. A great FPGA designer will always look at the data valid and empty flags. If the interface rates change, your design is robust enough to handle them without an FPGA re-spin.

With FPGA designs having easily 10 plus clock domains, it is ever important to pay attention and design ahead the FPGA clocking architecture. Use VISIO or a notebook, the point is put the keyboard down and prove to yourselves how you are going to synchronize all the data within that FPGA. This work lends to the old adage, ‘Ounce of prevention is worth a pound of cure’.

GSA Silicon Summit: More than Moore

The theme of this year’s GSA Silicon Summit is More than Moore. This has become a sort of catchall phrase for technologies other than simply moving to the next process node. The summit is on April 18th at the computer history museum (1401 Shoreline Blvd). Registration takes place at 9am and the actual sessions start at 9.45am. There are three panel sessions during the day and lunch is provided.

The first session, from 10-11am, introduced and moderated by Dan Rabinovitsj of Qualcomm, is on Disruptive Innovation — Enabling Technology for the Connected World of Tomorrow. The panelists are Jaga Jagannathan of IBM, Kiavan Karimi from Freescale, Mark Miscione of Peregrine, Naveed Sherwani of OpenSilicon and Ely Tsern of Rambus.

With the industry’s long-term focus on scaling now joined by functional diversification, this session will open with an overview on how More than Moore is enabling the connected landscape of today and shaping the future of tomorrow. The panel will then discuss current and emerging applications that continue to drive the More than Moore adoption as well as the process technologies enabling this development.

The second session, from 11.15am to 12.15pm, introduced and moderated by Ed Sperling is on How More than Moore Impacts the Internet of Things. On the panel are Jack Guedj of Tensilica (or maybe Cadence by then), John Heinlein of ARM, Kamran Izadi of Cisco and Oleg Logvinov from ST.

From the Swarm Lab to the smart bulb, the Internet of Things is showing evidence of becoming a reality. However today’s productivity trails what is needed to make the Internet of Things a truly ubiquitous system, and at the heart of the matter is developing the low power, mixed-signal technology that will enable chips and systems to communicate to the real world with minimal or without battery power. This session will open with an overview on where the industry stands in applying the concept of More than Moore to drive the Internet of Things. The panel will assess the industry requirements, obstacles, and advancements in developing the technology required to make the Internet of Things a reality.

After lunch is a third session, from 1.15-2.15pm, introduced and moderated by Bruce Kleinman of GlobalFoundries on Integration Challenges and Opportunities. The panellists are Jim Aralis of Microsemi, Misha Burich from Altera, William Chen from ASE, Steve Longoria of Soitec and Robert Rogenmoser of SuVolta.

Furthering the advancement of More than Moore involves unifying silicon technologies with novel integration concepts; application software convergence; and new supply chain business models. This session will open with an overview identifying the key industry trends, challenges and opportunities to realize higher density, greater functional performance and boosted power for ICs.

The panel will then discuss possible collaborative solutions to the challenges of integration and its impact on business market growth and investment.

The meeting wraps up at 2.30pm after some closing remarks. The full agenda with more detailed bios of the speakers is here with a link to the registration page. If you are a GSA member it is free, otherwise $50.

IC Test Debug at Altera

My background is IC design engineering, so it’s always a delight to talk with another engineer on their chip challenges. Today I spoke by phone with Sucharita Biswas, a Senior Hardware Engineer at Altera involved in IC test debug for FPGA devices.

Mentor Graphics User2User Conference

April 25, 2013, San Jose, CA

Click here to register.

Come hear Mentor Graphics CEO, Wally Rhines, 2013 Kaufman Award Winner,Chenming Hu, and Xilinx Senior VP,Victor Peng, at the User2User Conference in San Jose.

KEYNOTES

Organizing by Design

9:00am – 9:50am

Walden C. Rhines | CEO & Chairman | Mentor Graphics

Winning products are rarely the result of optimizing only one aspect of a design. Innovators generate success because they find ways to cross organizational and functional boundaries to optimize a product in multiple disciplines. Mature companies try to solve this problem by creating cross-disciplinary teams while startup companies do it naturally due to lack of enough resources to allow specialization. Meanwhile, products targeted at customers in different disciplines rarely appeal to more than one. Dr. Rhines has compiled data on cross-disciplinary product successes including attempts by companies to create products for hardware/software co-design, mechanical/electrical design integration and many more. He has identified successes and categorized the ways that companies have (rarely) achieved multi-disciplinary product optimization. He will use these examples to generate some guidelines for companies of all sizes to achieve product development success.

The New Era of Heterogeneous Architectures and Integration Technologies

10:00am – 10:50am

Victor Peng | Senior VP of Programmable Platform Group | Xilinx

Since the first integrated circuit was demonstrated in 1959, transistor density has increased by a factor of a billion and in the process has changed the world. However, despite the integration levels possible at advanced nodes like 28nm, the vast majority of high performance analog and high density memory chips have been and continue to be built with technologies distinct from high performance digital chips due to conflicting technology requirements. Another megatrend is the explosion in the cost of developing ICs in advanced nodes while the cost reduction benefit from moving to an advanced node has been disappearing. In this new era of integrated circuits the next wave of innovation will come in the form of heterogeneous architectures and products realized with 3D IC integration technologies. This talk will describe how Xilinx is enabling heterogeneous architectures and products as well as the underlying technologies required to realize them.

FinFET is a Beginning

1:00pm – 1:50pm

Dr. Chenming Hu | TSMC Chair Professor of Graduate School | Univ. of California, Berkeley

FinFET overcomes the impending show stopper that device physics imposes. The ultra-thin-body concept, which FinFET embodies, may lead to more new structures and materials research directions that can give relief for other future show stoppers such as the high cost of scaling by lithography. Dr. Hu is the 2013Kaufman Award winner for distinguished contributions to EDA.

TECHNICAL SESSIONS

Practical Tips to Increase Productivity and Communication with Calibre

11:00am – 11:30am

Joseph Davis | Marketing Director | Mentor Graphics

Just running physical or electrical verification is only part of the battle of getting your chip to Tape-out. We will show practical applications of how to minimize your debug time, minimize manual steps, and improve communications between team members and with your foundry. These applications are appropriate for both custom and digital design flows and leverage the Calibre tool set that you already own.

Meeting the Turn-Around Time Challenges for Sign-Off Extraction

11:30am – 12:00pm

Carey Robertson | Product Marketing Director | Mentor Graphics

Achieving design closure is increasingly difficult with new manufacturing effects creating modeling challenges and driving the need for additional interconnect corners at advanced nodes. Most customers are not using Calibre for Sign-Off Extraction. xACT SOC will change that and this session will introduce how this solution can accurately model interconnect at all nodes as well as achieve performance and scalability that is unmatched by competitive offerings.

Custom Place and Route Layout Enhancement Using Calibre with Timing Verification

2:00pm – 2:40pm

Shobit Malik | Senior Member Technical Staff | GLOBALFOUNDRIES

Christian Hauf | MTS< Member of Technical Staff | GLOBALFOUNDRIES

Sriram MAdhavan | PMTS, Principal Member of Technical Staff | GLOBALFOUNDRIES

Ahmed Mohyeldin | MTS, Member of Technical Staff | GLOBALFOUNDRIES

James Paris | Technical Marketing Engineer | Mentor Graphics

At advanced process technology nodes, design for manufacturability techniques like redundant via insertion and via line end extensions are known to be critical for improved yield and reliability. For digital designs, the router is used to insert redundancy in terms of more vias, large metal area as well as metal enclosure without growing area to make a design manufacturable. Since a router’s primary goal is to place and route a design in a limited amount of space, it is limited in its capability to push the insertion of redundant geometries. Hence, we use a custom solution whose primary focus is to insert a maximum of redundant geometries to make a design more manufacturable. These geometries are added within existing open space without growing existing space or touching existing layout using internally developed tool Y.E.S (Yield Enhancement Suite).

Since Y.E.S is a post place and route enhancement, it restricted us from verifying the timing impact as these changes are done on layout outside of the router’s database. This restriction limited the application of Y.E.S in the digital world since a proper sign off process required timing validation for all layout changes or enhancements done.

In this presentation we share our approach to use Y.E.S (or a similar post layout optimization tool) with the ability to back annotate it’s layout changes into a router’s database. We discuss the flow used to do this back annotation and show as an example our implementation where we imported these layout changes into MilkyWay database.

Layout Dependent Effects: Checking Number of Fingers with a Calibre-Based Flow

2:50pm – 3:30pm

Bruce Leong | Principal Hardware Engineer | Oracle

Starting with the 28nm process node, physics plays an even more important role in device performance. Layout practices must be changed in order to match modeling. Among these issues is matching the exact number of fingers for a device in the layout as specified by the circuit designer in the schematic. A method is described using Calibre LVS, the Query Server, a netlist flattener, and RVE output to achieve this matching.

Design Reliability with Calibre Smart-Fill and PERC

3:40pm – 4:20pm

Muni Mohan | Engineering Manager | Broadcom

This presentation dwells on improving design reliability and yield models with Calibre SmartFill and Calibre® PERC™.

The complexity of advanced technologies drives new requirements for poly/OD and metal fill to solve critical manufacturing effects, and more importantly design yields. New methodologies were developed for 28nm designs using Calibre SmartFill to meet the new strict DFM requirements while reducing run time, file size and iterations.

Besides manufacturing process, electrical rule checks can also significantly impact design yields & reliability. Identifying incorrectly configured devices, multi-power domain transition guides, and floating (leaky) gates is critically important right from the circuit stage, well before physical layouts. Such early design consistency checks written with rules in Calibre® PERC™ help us catch design mistakes early on, and validate some of our high reliability design metrics.

Both Calibre Smart-Fill and Calibre® PERC™ were significantly and successfully deployed on our largest 28nm tapeout recently.

Synopsys Laker Custom Layout and Calibre Interfaces: Putting Calibre Confidence in Your Custom Design Flow

4:30pm – 5:10pm

Dave Reed | Director of Marketing | Synopsys

Joesph Davis | Marketing Director | Mentor Graphics

While every design must pass sign-off before going to the foundry, it is inefficient to wait until the very end of the design process to run the sign-off checks. For this reason, Calibre provides interfaces to both custom and digital design tools which enable engineers to check against the sign-off decks throughout the design process. Through close cooperation between Mentor and Synopsys, Synopsys Laker users can check with Calibre “on the fly” during design to speed creation of design-rule correct layout, including electrically-aware voltage-dependent DRC checks.

For power and performance, Fins or BOXes?

I recently spoke to Arvind Narayanan, Product Marketing Manager for Mentor’s place and route division about emerging technology. This of course led to FinFETS, FDSOI, performance, power, and cost-benefit. The battle between FDSOI and FinFETs, said Narayanan, is going to be something to watch.

Both FDSOI and FinFET technologies provide better performance better power than bulk CMOS process. But, Narayanan asked, how do they compare with each other? Will FDSOI at 20nm bridge the 16nm finFET gap? Does finFET offer better cost benefits than FDSOI? The jury is still out on these questions, but he has some thoughts from a P&R perspective.

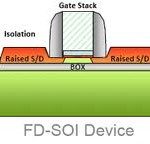

FDSOI technology relies on a thin layer of silicon that lays over a Buried Oxide (BOx). Transistors are built into the thin silicon layer, which is fully depleted of charges. Because the body is fully depleted the random dopant fluctuation that plagues bulk CMOS is reduced, thus improving performance even at lower VDD.

Some companies experimenting with FDSOI claim it has roughly 30% better performance, and lower power use, than bulk CMOS at 28nm.

28nm FDSOI is positioned as an alternate to bulk CMOS at 20nm. Narayanan said that if 28nm FDSOI delivers even half the power savings of bulk 20nm, it would be worth going that way to avoid dealing with the expense of double patterning (which is needed at 20nm). He pointed to another cost and scheduling benefit of 28nm FDSOI over 20nm FinFET from a P&R perspective; the FDSOI technology can use the conventional design flows and is completely transparent to the design tools.

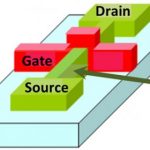

FinFET also promises the sun and the moon in terms of power, performance, and area. FinFET devices have their channels turned on their edge with the gate wrapping around them. The term “fin” was coined by professors at Berkeley to define the thin silicon conducting channel. This unique configuration of a gate wrapped around the channel on all three sides delivers much better channel control and better resistance to dopant fluctuations. The innovative 3D structure and tighter channel control does result in improved area, better performance, and lower power than bulk CMOS. Narayanan said that the P&R flows should be minimally affected by the adoption of FinFET devices, but that FinFET is more difficult to design and manufacture. FinFET technology is in production at 22nm and is quickly ramping up for the next generations.

Narayanan can’t predict whether one of these two technologies will actually become dominant, or if they both find a niche and co-exist successfully. As always, he said, production volumes with determine the eventual winner.

You can find related articles on foundry-based IC design and manufacturing at www.mentor.com/solutions/foundry.

RTL Restructuring

Hierarchical IC design has been around since the dawn of electronics, and every SoC design today will use hierarchy for both the physical and logical descriptions. During the physical implementation of an SoC you will likely run into EDA tool limits that require a re-structure of the hierarchy. This re-partitioning will cause a change to the logical hierarchy and require some functional verification re-runs.

Kathryn Kranen Wins UBM Lifetime Achievement Award 2013

UBM’s EETimes and EDN today announced Kathryn Kranen as the lifetime achievement award winner for this years ACE awards program. Kathryn, of course, is the CEO of Jasper (and is also currently the chairman of EDAC). Past winners exemplify the prestige and significance of the award. Since 2005 the award was given to Gordon Moore, then the Chairman emeritus of Intel, Wilf Corrigan, the Chairman of the board of LSI, Chung-Mou Chang the Founding Chairman of TSMC and Pasquale Pistorio the honorary Chairman of ST.

As CEO of Jasper, Kathryn has taken Jasper’s formal approaches to verification from a niche to a mainstream tool, managed to raise a round of funding in a very difficult environment, and put Jasper on the path to success.

Prior to Jasper, Kathryn was CEO of Verisity. While serving as CEO of Verisity Design, Kathryn and the team she built created an entirely new market in design verification. (Verisity later became a public company, and was the top-performing IPO of 2001, and subsequently was acquired by Cadence).

Prior to Verisity, Kathryn was vice president of North American sales at Quickturn Systems. She started her career as a design engineer at Rockwell International, and later joined Daisy Systems, an early EDA company. In 2009, Kathryn was named one of the EE Times’ Top 10 Women in Microelectronics. In 2012, she became a member of the board of trustees of the World Affairs Council or Northern California. She is currently serving her sixth term on the EDA Consortium board of directors, and was elected its chairperson in 2012. In 2005, Kathryn was recipient of the prestigious Marie R. Pistilli Women in Electronic Design Automation (EDA) Achievement Award. She graduated summa cum laude from Texas A&M University with a B.S. in Electrical Engineering.

You may know that over on the DAC websitewe are running a “my DAC moment” series of stories. Kathryn has set the bar so high that it is hard to beat. She got engaged at DAC. Here is her story:My favorite DAC memory: Las Vegas in 1996. I was working for Quickturn at the time, and my now-husband Kevin worked for Synopsys. On the Wednesday morning of DAC, Kevin “popped the question”, and I eagerly accepted his proposal. We then both rushed off to our various DAC meetings.

I was mesmerized by my diamond engagement ring, sparkling under the huge lights in the exhibit hall. It was great fun to share our happy news with hundreds of EDA friends and co-workers. That evening, some friends and Kevin and I looked for an Elvis wedding chapel, thinking a fake wedding photo would be a fun way to spring the engagement news on our parents. Alas, all the Elvis wedding chapels were booked *on a Wednesday!