Whoever has said that history never repeats itself should read this recent PR from AMD! The news can be summarized in three points:

- Multi-year agreement gives AMD access to a range of Synopsys design IP including interface, memory compiler, logic library and analog IP for advanced FinFET process nodes

- Synopsys acquires rights to AMD’s interface and foundation IP, and hires a team of engineers from AMD with IP R&D expertise

- These agreements enable AMD to realize ongoing engineering efficiencies and focus engineering efforts on product differentiation

The deal content is in these first two points: AMD can get access to the most expensive IP from Synopsys, because designed for advanced FinFET process nodes, in exchange, Synopsys will hire a team of IP expert engineers from AMD, and get rights for existing AMD’s interface and foundation IP. By the way, FinFET is such a wonderful process that the extra cost for IP compared with bulk is not negligible as I have heard about 1/3[SUP]rd[/SUP] more…

This deal is very similar with a previous deal between AMD and Virage Logic in 2008, when the IP vendor was paid by AMD with rights to PCI Express, USB or SATA IP instead of cash to compensate the memory compiler and logic libraries. Thanks to this deal, Virage Logic had entered into Interface IP market, 18 months before to be acquired by Synopsys for $315 million in cash. No design team was involved in the 2008 deal, but this came less than one year later, when “NXP transfer over 160 employees and the assets associated with selected advanced CMOS libraries, IP blocks and SoC architecture along with other classes of semiconductor IP”. In both cases, these deals have helped Virage Logic to quickly develop their IP port-folio, in particular by including Interface IP.

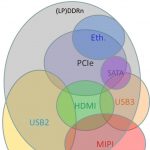

The above picture, extracted from the “Interface IP Survey” last version (Release 6), has been specifically designed for Semiwiki and Linkedin readers. This is a graphic view of the ASIC and ASSP design start for HDMI, SATA, PCIe, USB 2, USB 3.0, Ethernet, MIPI and DDRn memory Controller IP. If you look at a form (between a circle to an ellipse), the “diameter” (the larger lenght) is proportional to the total number of design starts including such IP function, internally developed or acquired from an IP vendor. In the real life, some SoC may integrate several IP, so the forms may recover each other. For example, we know that an Application Processor SoC may integrate MIPI, HDMI, USB 3.0 and LPDDRn. On the other hand, some of these interfaces are not supposed to be integrated in the same ASIC/ASSP, like Ethernet and MIPI, so the forms are not recovering. SATA is an exception: there are too few design starts, so the form is small and can’t recover with every protocol it should, and MIPI & PCIe should recover a little bit, but the forms are too far. That’s the model limitations, but the picture gives a good view of the respective adoption rate of the various protocols.

The largest by far is (LP)DDRn. If you agree with the System-on-Chip definition, an “IC integrating a Processor (CPU or GPU) core”, you realize that about 100% of the SoC will integrate a memory controller. The more intuitive definition linked to the word “system” suggests that a SoC will be at the hearth of an electronic system, so the chip is expected to “interface” with other IC and with the outside world. That’s the reason why the DDRn form is not only the largest but this recovering with most of the other forms, representing the interface protocols.

From a business point of view, we have shown in a previous post that these interface protocols have exhibited a very strong growth during the past 5 years, and are expected to grow again during the next 5 years. That’s why the rights for interface IP from AMD had a great value 5 years ago for Virage Logic and today for Synopsys. I should have a more precise figure in the next few days, but I suspect the IP business generated with the above mentioned protocols to reach between $900 million to $1 billion by 2020…

When traditional EDA business is almost flat since many years, you better understand why the interface IP “cake” can attract Synopsys and Cadence, and also why these two companies are heavy investors. I don’t think only about the acquisitions that both companies have done during the last three or four years. As a matter of fact, each of them is building a large engineering team, if I mention 1,300 engineers, only dedicated to Design IP for Synopsys, I am probably below the real number as of today (certainly in fact, as this number does not take into account the above mentioned team from AMD). I guess that we can expect to soon get IP related news from Cadence…

You may find additional information here and the Table of Content for “Interface IP Survey 2010-2013 – Forecast 2014-2020” will be available soon (you may contact me through Linkedin if you want to receive it as soon as it will be completed).

Eric Esteve from IPNEST