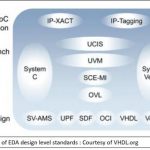

HDL languages are a matter of engineering personal preference and often corporate policy dictates which language you should be using on your next SoC design. In the early days we used our favorite text-based editor like Vi or Emacs, my choice was Vi. The problem with these text-based editors of course is that they really don’t understand that you’re using an HDL, so they don’t check for the most common syntax requirements, which leads to lots of iterations of finding and fixing typos and syntax errors. Engineers have more important work to accomplish than iterating the HDL design entry.

In the web world when coding with CSS, Javascript and HTML5 languages we can use a beautiful IDE like Dreamweaver from Adobe to color code the keywords, match braces, and in general speed up the design entry task. Likewise, in the HDL world we have a similar IDE from Sigasi in their product called Sigasi Studio. To get an update I had an email chat with Hendrik Eeckhaut.

Q: What’s happening with designers choosing to code with SystemVerilog these days?

Most SystemVerilog users have a love/hate relationship with SystemVerilog. This hardware description and verification language is really powerful, but also really complex. It is an extremely big language and it does not protect you at all from making mistakes. So SystemVerilog users will benefit even more from the assistance that Sigasi Studio offers, than their VHDL colleagues. Sigasi Studio helps you focus on what is really important, the design, instead of loosing time making the compiler understand your intentions.

Q: So Sigasi started out with an IDE for VHDL, how did that help with SystemVerilog?

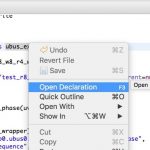

Based on Sigasi’s experience with providing excellent VHDL support, the Sigasi development team knew how to tackle most challenges in providing a good development environment for SystemVerilog: immediate feedback about syntax errors, autocomplete, open declaration, and so on. And because Sigasi studio understands what SystemVerilog means, you get very accurate feedback.

Q: What helps me code in SystemVerilog faster?

The biggest technical challenge was providing good support for SystemVerilog’s Preprocessor. The preprocessor does a textual transformation of SystemVerilog source files. So it can completely rewrite the code that goes into the actual compiler. This preprocessor is stateful and depends on the compilation order. This makes it difficult to keep track of what exactly is going on. To remedy this, Sigasi Studio 3.5 provides features to easily inspect or preview preprocessed code:

- Source code that is excluded with the Preprocessor is automatically grayed out in the editor.

- The result of Macro’s can be easily previewed in an addition view, or simply by hovering your mouse over the macro.

- Syntax errors are immediately reported

Q: When I code a large design there are plenty of include files, how is that supported in your IDE?

Another example of how Sigasi Studio helps SystemVerilog users, is “include files”. A typical pattern in SystemVerilog is to include sources into other source files (with the Preprocessor). In this case the included file can see everything in the scope of the including file. With an ordinary editor, you have to think about all of this yourself. With Sigasi Studio however, this information is available whenever you require it. For example during autocompletes. And the nice thing is, this does not require any additional setup. Again, this allows you to focus on the real job: getting your design ready, or making sure it is well tested.

Q: If I want to give Sigasi Studio a quick test, what should I do?

If this has triggered you to try Sigasi Studio on you own SystemVerilog designs, you can request a full trial licenseon our website www.sigasi.com. This enables you to try all Sigasi Studio’s features on your own projects and feel how Sigasi empowers you. And please tell us all about your experience.

Related blogs