Over the holidays I did an interview with CNBC on the subject of Qualcomm. The producer had read the History of Qualcomm chapter in our book Mobile Unleashed and wanted to base a 15 minute report on it. The interview lasted 90 minutes but of course only snippets of what I said were used. You can see the recorded report by clicking on the image below. You can also see the history of Qualcomm chapter HERE for reference.

Before you judge, here is the other 90 minutes of the interview as I remember it:

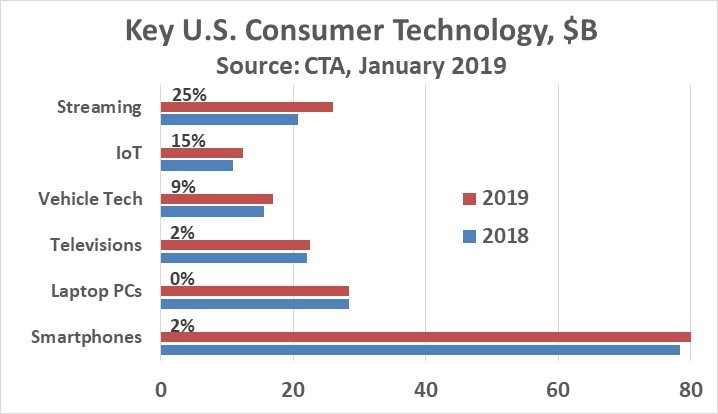

I started out talking about the fabless semiconductor transformation during the 1980s and 1990s when Qualcomm was one of the leaders. If not for Qualcomm we would not have the mobile electronics we have today. Qualcomm also perfected the multi sourcing foundry business model which is critical since competition is what drives our industry. Competition is what enables low cost consumer electronics and made it possible for us to have super computer class devices in our pockets, absolutely.

I remember working with QCOM down to 40nm when their chips were being manufactured at TSMC, UMC, SMIC, and Chartered. QCOM would design first on TSMC using special design rules and design practices that enabled multi manufacturing sources. Most other companies did this as well but QCOM was the best at it for sure. TSMC was not happy about this of course since they did all of the heavy process technology lifting only to lose high volume manufacturing business to the other foundries but that was foundry life back in the 1980s and 1990s.

On the business side however, QCOM was very anti-competition. QCOM started out as a systems company making navigation and communication systems. QCOM then pivoted into a chip maker and more importantly a patent strong-hold based on those chips. In fact, QCOM has always made more money from licensing patents than chips. The reason being is that they adopted a “no license – no chip” business model. So you had to license the patents if you wanted a QCOM chip. QCOM was the only game in town for modems and leading edge SoCs at the time so they could play the chip game by their own rules.

Buying commercially available chips to launch products then over time developing your own chips is a critical part of the semiconductor ecosystem if you are a consumer electronics company. Smartphone giants like Apple, Samsung, and Huawei do this for a couple of reasons: Price of course, at high volumes you can make your own chips cheaper than buying them. You can also more easily differentiate features from your competitors. Battery life is one example. The less chips you have in your device the longer the battery life. If you look at the iPhone tear-downs over the years you will see supporting chips disappear into the SoC on a regular basis thus saving power and space. The modem however remains a separate chip in Apple phones.

The other big advantage of making your own chips is prototyping and emulation. As you develop your chip you can verify it quickly using prototyping and you can also start software development months before the chip is done. This is a huge advantage for smartphone companies that control their own software ecosystem like Apple.

Bottom line: Controlling your silicon really is required to be a leader in consumer electronics.

The problem is that to buy a QCOM chip you also had to license the patents which made it much more difficult to develop your own chips without getting letters from QCOM legal. QCOM pricing was also a problem. For the license and chip QCOM got a percentage of the smartphone rather than a fixed chip price. That’s like going to the grocery store and the final item you pay for is a percentage of what you already have in the bag. Having been in the IP business myself I was both amazed and impressed that QCOM got away with this. It really was a disruptive business model for fabless semiconductor companies.

As it turns out it was a bit too disruptive. The U.S. and other governments have accused Qualcomm of unfairly competing and charging excessive rates for its technology. China, Korea, Taiwan, and the EU have already fined or settled with QCOM. The US case is in progress now. I would be very surprised if the FTC did not get a favorable first ruling but we shall see. Hopefully there will be a quick settlement so we can all get back to the business at hand and that is making semiconductors for the greater good of consumer electronics.

This is just my opinion of course. I don’t have financial ties to either company but I do own an iPhone 10. I don’t particularly care for it. The one nice thing I can say is that the battery lasts MUCH longer than previous iPhones. I can now get through a full day of use without charging which is a nice change. The excessive price however is a bit disruptive and at some point in time Apple may pay dearly for that as well.

Update:

The FTC rested their case against QCOM and in my opinion it was much weaker than expected. QCOM is presenting their defense followed by closing arguments but as of today I don’t think the FTC made their case. Opinions are split of course. In fact a hedge fund shorted QCOM stock expecting a big verdict for the FTC:

Qualcomm Incorporated: Ignoring The Legal Risk Is Patently Ridiculous

“The FTC has brought a powerful legal case against the company, and the trial [conducted entirely before a judge, not a jury] is currently underway,” the note said. “We believe Qualcomm will lose.”

If you want to follow the case Twitter is a good place to start: #FTCQCOM