For decades, semiconductor teams have relied on traditional methods such as corner-based analysis, surrogate monitors, and population-level statistical screening for post-silicon validation. These methods served well when variability was modest, and timing paths behaved predictably. However, today’s advanced nodes and complex architectures expose the limitations of these approaches. Local process variation, workload-driven activation, dynamic voltage droop, aging, and subtle defects create path-specific outcomes that traditional monitors cannot capture. Proxy monitors cannot reflect real functional paths under real operating conditions, leaving engineers blind to critical performance, quality, and reliability issues.

As competition and time-to-market pressures increase, teams cannot afford the iterative cycles required to reconcile design assumptions with actual silicon behavior.

proteanTecs recently hosted a webinar addressing this very topic and presented its solution for accelerating New Product Introduction (NPI). proteanTecs’ Alex Burlak, Executive Vice President, Test and Analytics and Noam Brousard, Vice President, Solutions Engineering led the webinar session. The webinar titled “Accelerating NPI with Deep Data: From First Silicon to Volume” presented a new approach that replaces assumptions with real-time, on-chip insight, enabling teams to detect issues early, characterize power/performance confidently, accelerate debug, and optimize qualification.

The Need for Deep Visibility Across the NPI Lifecycle

Modern NPI requires visibility into every chip, in every scenario. Engineers need to understand where individual devices might fail, how variability affects functional paths, and how workload, voltage, and temperature interact to create real operational limits. Traditional methods cannot provide this insight, leaving teams reactive and slow to identify critical issues. This webinar demonstrated that high-resolution, chip-specific data allows teams to characterize actual performance, detect early parametric drift, and unify insights across design, test, and validation phases.

On-Chip Monitoring with Advanced Design-Aware Analytics

proteanTecs provide a HW IP Monitoring system that includes monitoring agents and an infrastructure that provides the control framework. The on-chip agents are embedded, ultra-lightweight on-chip monitors engineered to extract “deep data” – including design profiling, material classification, performance degradation, workload impact, and operational effects. Rather than monitoring only high-level counters or traditional test structures, these agents sit close to the actual circuitry, collecting granular telemetry throughout the chip’s entire operational life.

By capturing this deep data from within the device and applying advanced machine learning, these agents enable early detection of reliability risks, performance drift, power inefficiencies, and system degradations, long before they become visible at the system level.

Timing Margin Monitoring: Real-Time Insight from Real Functional Paths

proteanTecs Margin Agents deliver this visibility by embedding lightweight monitors directly into real timing paths. These agents measure instantaneous slack and are sensitive to operational conditions, process variations, aging, and latent defects. Unlike proxy circuits, they capture the real limits of a chip, providing precise insight into performance and reliability boundaries.

Alex Burlak opened the webinar with a use case demonstrating how proteanTecs enables customers to correlate simulation expectations with real silicon behavior.

By aggregating agent data from multiple test stages including wafer sort, final test, and system-level evaluation into a centralized analysis environment, engineers can directly align design intent with silicon results.

By examining process signatures captured by Profiling Agents across standard cells, teams can quantify process variation relative to design corners and link it to metrics such as Fmax, VDDmin, and the impact on yield. This insight supports detailed root-cause analysis, helping engineers identify why certain chips run faster or slower and isolate variation sources, such as clock-path versus data-path effects or on-chip variation (OCV).

To accelerate characterization, proteanTecs offers a Smart Material Selection algorithm. After initial test data collection, this algorithm identifies the most representative subset of chips (e.g., 50 out of 1,000) that best captures process variability. By focusing on these representative devices, characterization efforts, such as voltage, temperature, or workload sweeps, become far more efficient and comprehensive. Advanced HTOL Methodologies for Device Qualification.

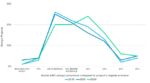

Next, Alex presented a use case on High-Temperature Operating Life (HTOL) testing. Using proteanTecs’ Profiling and Margin Agents, customers can track degradation over time, collecting data at intervals such as 0, 48, 500, and 1,000 hours. This enables quantification of parametric drift and more accurate decisions about guard-banding and reliability.

Unifying Data from Design, Test, Validation, and Characterization

proteanTecs’ agents produce consistent, high-resolution data throughout the NPI lifecycle. Engineers can trace performance trends from wafer sort through ATPG, functional testing, HTOL, qualification, and high-volume production. They can even continue monitoring in the field. This unified dataset allows teams to detect deviations early, correlate results across test stages, and communicate insights efficiently between design and product engineering teams. By grounding decisions in actionable data rather than assumptions, organizations reduce risk and accelerate time-to-market.

Smart Models: Eliminating Yield–Quality Trade-Offs

The webinar highlighted smart models that leverage agent data to resolve the traditional trade-off between yield and quality. Instead of relying on global statistical thresholds, smart models analyze each chip against its expected electrical behavior. They identify true outliers based on high-resolution, chip-specific measurements, avoiding the need to discard potentially good devices or compromise quality. Noam emphasized that this approach allows teams to maintain high yield without sacrificing reliability, effectively providing both efficiency and assurance across production.

Continuous Monitoring during HTOL and In-Field Monitoring

The solution also supports continuous monitoring during HTOL and in-field operation. Engineers can observe degradation trends in real time, rather than waiting for post-stress readouts. Noam demonstrated that this enables early detection of unexpected behavior, identification of hotspots, and rapid response to process or setup issues. In-field operation benefits similarly: Margin Agents operate without interrupting workloads, providing continuous visibility into aging, performance drift, and reliability over the product’s lifetime. By extending NPI insight into actual deployment, teams can react proactively, reducing risk and improving long-term product performance.

Summary

Alex and Noam demonstrated through live demos on case studies that deep on-chip data transforms NPI by providing real-time, high-resolution insight into each chip’s power, performance and reliability. On-chip agents reveal true performance limits, smart models identify outliers without compromising yield, and continuous monitoring provides actionable information from wafer sort through in-field operation.

By embedding deep data and analytics into the NPI workflow, semiconductor teams gain confidence, clarity, and control. Every chip becomes its own source of truth, and every stage of the NPI pipeline benefits from actionable insight. The result is faster ramp, higher quality, fewer surprises, and a fundamentally more predictable transition from first silicon to volume production.

To watch the on-demand webinar, click here: https://hubs.la/Q03W0k2V0

To learn more, visit:

Also Read:

Failure Prevention with Real-Time Health Monitoring: A proteanTecs Innovation