There is one semiconductor company that for the last 3 years has outperformed ARM and more than doubled in stock price relative to Apple. They are everywhere but barely known to most. The success of this company in the coming year though could result in the leveling of AMD and nVidia as they try to adjust to the economics of the mobile Tsunami, which means the commoditization of application processors. The company is Imagination Technologies, whose graphics IP is in many mobile processors including Apple’s ARM family and Intel’s latest Atom processors.

Clayton Christensen described in his book the Innovators Dilemma the difficulty and reluctance that companies have of going into new markets that effectively cannibalize existing high margin businesses. One of the examples that Christensen focuses on is the disk drive industry in which every few years a new leader would emerge to displace the previous leader who was focused on maximizing its market share and profits instead of forging ahead with an eventual replacement. One of the key drivers of the replacement was a smaller form factor device (higher density was always understood to be a requirement).

What happens however, to Christensen’s model when in the midst of a massive increase in graphics capability there is a clash with an even greater force called personal mobility (or ultra mobility). The shift from desktop to notebook happened over many years and was considerably more gradual than what we have seen in just the last 4 years when the Internet was placed in the palm of one’s hand with the Smartphone. The first order of business for Apple, Samsung, HTC and others has been to shoehorn all the electronics in an area that has no tolerance for excessive heat. Something had to give.

Open any souped-up desktop PC with the latest AMD or nVidia graphics card and you realize that the cooling infrastructure has overshot that of the processor and indeed it is a supercomputer. The massive R&D budgets employed by AMD and nVidia are intended to win the gamers and then over a couple of Moore’s Law generations trickle down to the notebook, tablet and then Smartphone.

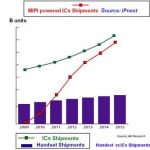

In typical, Innovator’s Dilemma fashion, Imagination Technologies has come from the ground up to challenge AMD and nVidia’s from the rear in an area that both are trying to catch up. This will be difficult for both to do because of the head start that Imagination Technologies has had in licensing its technology to Apple, Intel, Qualcomm, TI and Samsung. Indeed ARM feels threatened. Against this array of competitors, nVidia sits alone. The company has seen revenue more than double over the past three years and operating profit margins exceed that of AMD and nVidia by a wide margin. You could say that the Innovator’s Dilemma formula has been extended to take into account how an IP business model is superior to a Fabless Business Model.

Intel’s push in the very slim ultrabook form factor is already reducing nVidia and AMD’s share in the PC space. With Imagination Technologies licensing its graphics technology to the Fab players (Intel, Samsung and yes Apple – I consider them virtual fab) there is a squeeze on nVidia and AMD from above and below. All of this was driven by a major form factor shrinkage in PCs and Smartphones that was unforeseen just a few years ago but is dramatically reshaping the industry.

For AMD to survive, I believe they have to become an IP design House for Google, Samsung, Qualcomm, Amazon, HTC or other major player. Pure Fabless, with no shared investment, is no longer a model that survives up against the Fab Titans: Intel and Samsung. Companies must move to one side or the other: IP House or Fab Focused. If I can make a play of words on Jerry Sanders famous quote: Real Men Have Fabs or Real Men Live in IP Houses.

I find it interesting that in all of this transformation, Intel has decided that it needs Imagination Technologies for its low end Atom. Another sign that Paul Otellini believes Intel’s future value is really based on process technology and not chip architectures. Intel has never been able to keep up with nVidia on graphics but it way outperforms TSMC in process development. Imagination Technologies is able to give nVidia a run for its money in the graphics space and as a result have outperformed them financially. As a comparison over the past three years, nVidia’s revenue has been flat and is down since 2007 – perhaps a sign that the cliff is near.

FULL DISCLOSURE: I am Long AAPL, INTC, QCOM, ALTR