VLSI Technology, for those of you not of a certain age, was one of the companies that, along with LSI Logic, created the ASIC business. One challenge in ASIC is that the customer needs to decide which ASIC company to use (since the libraries and technologies are all different) meaning they needed to get quotes from several companies.… Read More

Tag: webinar

Amorphous Silicon and TFTs

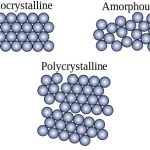

Most ICs are fabricated with crystalline silicon (c-Si), which is a tetrahedral structure forming a well-ordered crystal lattice. There’s another form of semiconductor material called amorphous silicon (a-Si) which has no long-range periodic order. It turns out that a-Si is a great material for the active layer in thin-film… Read More

Adding a Digital Block to an Analog Design

My engineering background includes designing at the transistor-level, so I was drawn to attend a webinar today presented by Tanner EDAand Incentia about Adding a Digital Block to an Analog Design. Many of the 30,000 users of Tanner tools have been doing AMS designs, so adding logic synthesis and static timing analysis from Incentia… Read More

Finding Logic Issues Early that Impact Physical Implementation

Complex SoC project teams typically use a divide and conquer approach where specialized engineers work in separate domains, like front-end or back-end. The five major engineering tasks for IC design can be described as: RTL design, synthesis, floor planning, place and route, then finally design analysis.

What if you could detect… Read More

Designing SmartCar ICs

When I upgraded cars from a 1988 to 1998 Acura it seemed like my car had become much smarter with a security chip in the key, security codes in the radio and a connector for computer diagnosis, however in today’s modern auto there’s a lot more mixed-signal design content. Micronasand Synopsysgot together and hosted … Read More

SiC and Si Power Devices

ICs for consumer electronics are often battery powered, which are considered low voltage designs. On the other end of the IC spectrum are high voltage devices used in many industrial applications like: automotive, aerospace, data centers, transportation and power generation. … Read More

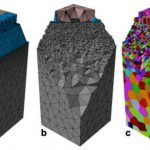

TCAD to SPICE Simulation of Power Devices

The periodic table shows that Silicon (Si) is in a column along with other elements like Carbon (C) and Germanium (Ge). With so much emphasis on Silicon, you’d think that the other semiconductor materials have been neglected a bit.

Silicon is a wonderful material and most of our consumer electronics and handheld devices … Read More

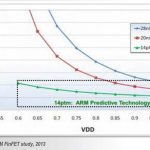

FinFET Design for Power, Noise and Reliability

IC designers have been running analysis tools for power, noise and reliability for many years now, so what is new when you start using FinFET transistors instead of planar transistors? Calvin Chow from ANSYS (Apache Design) presented on this topic earlier in the summer through a 33 minutewebinar that has been archived. There is… Read More

Improving Complex System Design

Next week Mike Jensen of Mentor will present a webinar Improving Complex System Design Reliability and Robustness. The webinar will be presented live twice and presumably available for replay soon after, as is usually the case:

- September 4th 6.00-6.45am pacific (9pm in Asia, 3pm in most of Europe)

- September 4th 10.00-10.45am

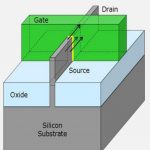

FinFETs for your Next SoC

Planar CMOS processes have been offered for decades now, and all the way down through the 28nm node it has been riding the benefits of Moore’s Law. A few years back we started hearing from Intel about TriGate (aka FinFET) starting at the 22nm node as a way to use a more 3D processing approach for transistors instead of planar CMOS.… Read More