Formal verification methods are being adopted at a fast pace as a complement to traditional verification methods like functional simulation for IP blocks in SoC designs. I had a video meeting with Max Birtel, co-founder of LUBIS EDA and learned more about their history, products and vision. This company started recently in 2020… Read More

Tag: vip

Truechip Introduces Automation Products – NoC Verification and NoC Performance

While Truechip has established itself as a global provider of verification IP (VIP) solutions, they are always on the lookout for strategic IP needs from their customer base. Over the last several years, a solid market for Network-on-Chip (NoC) IP has grown, driven by the need to rapidly move data across a chip. Concurrently, the… Read More

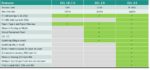

Verification IP Hastens the Design of CXL 3.0

Although version 2.0 of the Computer Express Link (CXL) standard is just making it into new designs, the next generation, version 3.0, has been approved and is now ready for designers to implement the new silicon and firmware needed to meet the new standard’s performance specifications. CXL, an open industry-standard interconnect,… Read More

Truechip: Customer Shipment of CXL3 VIP and CXL Switch Model

The tremendous amount of data generated by AI/ML driven applications and other hyperscale computing applications have forced the age old server architecture to change. The new architecture is driven by the resource disaggregation paradigm, wherein memory and storage are decoupled from the host CPU and managed independently… Read More

Truechip’s DisplayPort 2.0 Verification IP (VIP) Solution

Integrating IP to build SoCs has been consistently on the rise. Growth in complexity and meeting time to market pressures are some primary drivers behind this phenomenon. Consequentially, the IP market segment has also been enjoying tremendous growth. While this is great news for chip design schedules, it does highlight the … Read More

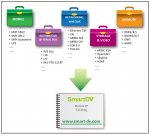

Design and Verification IP: Insights From a SmartDV Insider

Just as SmartTV has become a household term, SmartDV has become a well-known name within semiconductor design and verification circles. SmartDV™ Technologies is the proven and trusted choice for Smart Design IP and a range of Verification Solutions™ from Verification IP, including assertion-based and post-silicon validation… Read More

Avery Levels Up, Starting with CXL

Let me acknowledge up front that Avery isn’t the most visible EDA company around. If you know of them, you probably know their X-propagation simulator. Widely respected and used, satisfying a specialized need. They have also been quietly building over the years a stable of VIPs and happy customers, with a special focus on VIPs for… Read More

Verification IP for Systems? It’s Not What You Think.

When I think of verification IP (VIP), I think of something closely tied to a protocol standard – AMBA, MIPI or DDR for example. Something that will generate traffic and run protocol compliance checks, to verify correct operation of an IP or as a model to use in SoC verification. What would a VIP for systems be? Systems support multiple… Read More

The Quiet Giant in Verification IP and More

In the technology industry, we’re all used to the hype about the latest and greatest. Semiconductor IP participates in the over-drive news cycle from time to time as well. So, when I see a company that has real, solid credentials but has resisted the temptation to over-hype, it gets my attention. I had an experience like this recently… Read More

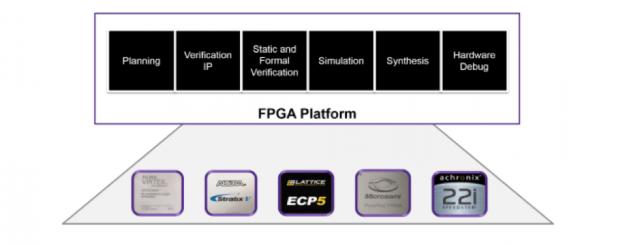

When FPGA Design Looks More Like ASIC Design

I am sure there are many FPGA designers who are quite content to rely on hardware vendor tools to define, check, implement and burn their FPGAs, and who prefer to test in-system to validate functionality. But that approach is unlikely to work when you’re building on the big SoC platforms – Zynq, Arria and even the big non-SoC devices.… Read More