Imagine how semiconductor design sizes leapt higher with automation in digital design, which started from standard hardware languages like Verilog and VHDL; analog design automation is still catching up. However, it was not without a significant effort put in moving designers from entering schematics to writing RTL, which… Read More

Tag: verification

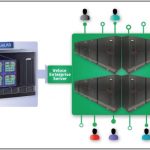

5 Verification Challenges of IoT Solved by Emulation

Software-centric Emulation environment takes the forefront in modern SoC verification. As more and more devices are IoT enabled, the SoCs have to make special provisions to factor many things including communication, power usage, and network switching, and so on. Also, the demand for an SoC (specifically for smartphone which… Read More

Pushing on AXI-connected IP in FPGAs

Success stories are great. Reading how someone uses a product contributes much more insight than reading about a product. Last month we had a teaser for a presentation by Wave Semiconductor; this month, we have the slides showing how they are using FPGA-based prototyping, AXI transactions, and DPI to speed up development.

First,… Read More

Perfecting the Great Verification Fugue

Michael Sanie (Senior Director Marketing in the Synopsys Verification Group) gave the wrap-up presentation at SpyGlass World recently, on the Synopsys Verification Direction. I learned from an interview Michael gave to Paul McLellan that he is an accomplished pianist. I’m a pianist also, though of considerably less talent,… Read More

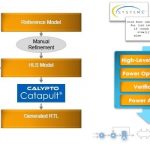

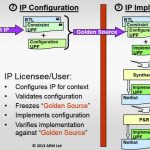

Shifting Low Power Verification to an IP to SoC Flow

One of the most exciting recent developments in low power design and verification is the successive refinement flow developed by ARM® and Mentor Graphics®.… Read More

A Connectivity Verification Idea

A Wirble

In case you hadn’t noticed, I like to write from time to time about EDA product ideas. I assume these are somewhat original, but given the maxim “there’s nothing new under the sun…”, I may well be wrong. In any event, I like to share these ideas if only to demonstrate that innovation in EDA is not stalled because we’ve run out big,… Read More

Something Old, Something New…EDA and Verification

When I got the opportunity to blog about verification, I thought, what new and interesting things should I talk about? Having started my EDA career in 1983, I often feel like one of the “oldies” in this business…remember when a hard drive required a static strap, held a whopping 33 MB, and was the size of a brick? Perhaps they should … Read More

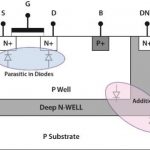

Together At Last—Combining Netlist and Layout Data for Power-Aware Verification

The market demanded that gadgets it loves become ever more conscious of their power consumption, and chip designers responded with an array of clever techniques to cut IC power use. Unsurprisingly, these new techniques added to the complexity of IC verification. When you’re verifying a design that has 100+ separate power domains,… Read More

A Brief History of FPGA Prototyping

Verifying chip designs has always suffered from a two-pronged problem. The first problem is that actually building silicon is too expensive and too slow to use as a verification tool (when it happens, it is not a good thing and is called a “re-spin”). The second problem is that simulation is, and has always been, too slow.

When Xilinx… Read More

Michael Sanie Plays the Synopsys Verification Variations

I met Michael Sanie last week. He is in charge of verification marketing at Synopsys. I know him well since he worked for me at both VLSI Technology and Cadence. In fact his first job out of college was to take over support of VLSIextract (our circuit extractor), which I had written. But we are getting ahead.

Michael was born in Iran and… Read More