Dr. Stanley Hyduke founded Aldecin 1984 and their first product was delivered in 1985, named SUSIE (Standard Universal Simulator for Improved Engineering), a gate-level, DOS-based simulator. The SUSIE simulator was priced lower than other EDA vendor tools from the big three: Daisy, Mentor and Valid (aka DMV). Aldec maintains… Read More

Tag: verification

Aldec-Altera DO-254

As described in DO-254, any inability to verify specific requirements by test on the device itself must be justified, and alternative means must be provided. Certification authorities favor verification by test for formal verification credits because of the simple fact that hardware flies not simulation models. Requirements… Read More

IP Wanna Go Fast, Core Wanna Not Rollover

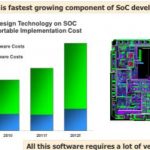

At a dinner table a couple years ago, someone quietly shared their biggest worry in EDA. Not 2GHz, or quad core. Not 20nm, or 450mm. Not power, or timing closure. Call it The Rollover. It’s turned out to be the right worry.

Best brains spent inordinate hours designing and verifying a big, hairy, heavy breathing processor core to do … Read More

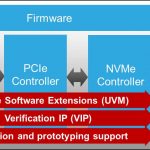

Shorter, better and easier PCIe and NVM Express Verification flow with advanced technologies

We have talked about Cadence subsystem IP strategy, illustrated by NVM Express subsystem IP, in a previous blog. What we said was that “A subsystem IP based approach will also speed up the software development and validation phase: if the IP provider is able to propose the right tools, like the associated Verification IP (VIP), … Read More

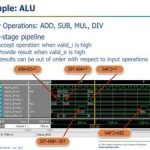

Scoreboards and Results Predictors in UVM

If verification is the art of determining that your design works correctly under all specified conditions, then it is imperative that we are able to create an environment that can tell you if this is truly the case.

Scoreboards are verification components that determine that the DUT is working correctly, including ensuring that… Read More

How many languages an Engineer should speak?

I speak VHDL and SystemC, others speak Verilog and SystemVerilog … what do you speak?

Before getting into the core of the topic let me give you some round figures, engineers love numbers. Julian Lonsdale “European Sales Manager at Aldec” informed me at the Xfest Munich last month that Aldec carried out a survey to evaluate the usage… Read More

Achieving Rapid Verification Convergence of ARM® AMBA® 4 ACE™ Designs using Discovery™ Verification IP

Synopsys is consolidating the company positioning on Verification IP. We have announced the launch of Discovery VIP in Semiwiki, in February this year, and we have commented about the acquisition of nSys and ExpertIO in January. This webinar, “Achieving Rapid Verification Convergence of ARM® AMBA® 4 ACE™ Designs using Discovery™… Read More

Mentor’s New Emulator

Mentor announced the latest version of their Veloce emulator at the Globalpress briefing in Santa Cruz. The announcement is in two parts. The first is that they have designed a new custom chip with twice the performance and twice the capacity. It supports up to two billion gate designs and many software engineers. Surprisingly … Read More

Kathryn Kranen Interview in San Jose Mercury News

There is an interview in the San Jose Mercury News with Kathryn Kranen, Jasper’s CEO. Of course the Mercury is a general newspaper and can’t expect most of its readership to have a clue what EDA is, never mind formal verification. It’s a similar problem to the one we all have when we try and explain to our families… Read More

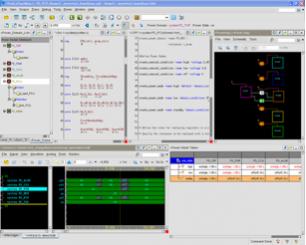

Verdi’s 3rd Symphony

The first version of the debug platform Verdi (then called Debussy) dates back to 1996 over 15 years ago. The second version was released in 2002. And now SpringSoft is releasing the 3rd version Verdi[SUP]3[/SUP]which is a completely new generation. A tool environment like Verdi seems to need to be completely refreshed about every… Read More