Today, an SoC can have multiple instances of an IP and also instances of many different IPs from different vendors. Every instance of an IP can work in a separate mode and requires a dedicated power arrangement which may only be formalized at the implementation stage. The power intent, if specified earlier, will need to be re-generated… Read More

Tag: upf

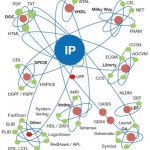

An Universe of Formats for IP Validation

Although I knew about Crossfire’s capabilities for signing off quality of an IP before its integration into an SoC, there was much more to learn about this tool when I visited Fractal Technologies booth during this DAC. The complexity handled by this tool to qualify any type of IP for its integration into an SoC can be imagined by the… Read More

Fractal at DAC 2015 – What’s new?

I have been observing Fractal Technologiesexhibiting at DACyear after year, and every year they have demonstrated good value added features in their tools for SoC and IP development. This year at 52[SUP]nd[/SUP] DAC Fractal’s booth number is 1110. Earlier in this year Fractal had added a new ‘Cdiff’ feature in its flagship product… Read More

A Comprehensive Power Optimization Solution

In an electronic world driven by smaller devices packed with larger functions, power becomes a critical factor to manage. With power consumption leading to heat dissipation issues, reliability of the device can be affected, if not controlled or the device not cooled. Moreover, for mobile devices such as smartphones or tablets… Read More

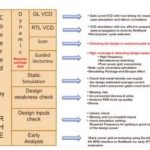

A Complete Scalable Solution for IP Signoff

In an SoC world driven by IP, where an SoC can have hundreds of IP (sourced not only from 3[SUP]rd[/SUP] party but also from internal business units which can have a lot of legacy) integrated together, it has become essential to have a comprehensive and standard method to verify and signoff the IP. Additionally, these checks must … Read More

Design & EDA Collaboration Advances Mixed-Signal Verification through VCS AMS

Last week it was a rare opportunity for me to attend a webinar where an SoC design house, a leading IP provider and a leading EDA tool provider joined together to present on how the tool capabilities are being used for advanced mixed-signal simulation of large designs, faster with accuracy. It’s always been a struggle to combine design… Read More

Active Power Management in UPF Using SPICE, VHDL-AMS or Verilog-AMS

My former co-worker, Kenneth Bakalar at Mentor Graphics is an expert in AMS modeling languages and UPFmethodology, so he recently teamed up with Eric Jeandeau to author an interesting white paper: Interpreting UPF for a Mixed-Signal Design Under Test. This white paper is based on a presentation made at DVCon earlier this year.… Read More

A Tool Conceived With Designers’ Input and Developed from Scratch

If we look at the past, most of the EDA tools in the semiconductor design space have originated from a designers’ need to do things faster. Regardless of whether it is design exploration, manual design, simulation, verification, optimization (Power Performance Area – PPA) and many other steps in the overall design flow.… Read More

2013 Awards, and the Winner is…Power

Of all the things that designers have to worry about in the power-performance-area (PPA) equation, the most challenging is power. SoCs have reached a point that we can put a lot of stuff on them, but if we are not careful we cannot light it all up at once. Dark silicon, where we put subsystems on a chip but then don’t have enough … Read More

How to Assure Quality of Power and SI Verification?

As power has become one of the most important criteria in semiconductor design today, I was wondering whether there is a standard set for the power verification for an overall chip. We do have formats evolved like CPF and UPF and there are tools available to check power and signal integrity (SI), however I don’t see a standard objective… Read More