I think by now all of us know, or have heard about 20nm process node, its PPA (Power, Performance, Area) advantages and challenges (complexity of high design size and density, heterogeneity, variability, stress, lithography complexities, LDEs and so on). I’m not going to get into the details of these challenges, but will ponder… Read More

Tag: tsmc

Why Adopt Hierarchical Test for SoC Designs

IC designers have been creating with hierarchy for years to better manage large design sizes, however for the test world the concept of hierarchy and emerging standards is a bit newer. TSMC and Synopsys jointly created a webinarthat addresses hierarchical test, so I’ve attended it this week and summarized my findings here.… Read More

450mm Wafers are Coming!

The presentations from the 450mm sessions at SEMICON West are up now. After talking to equipment manufacturers and the foundries I’m fairly confident 450mm wafers will be under our Christmas trees in 2016, absolutely. TSMC just increased CAPEX again and you can be sure 450mm is part of it. SEMI has a 450mm Central landing page HERE… Read More

TSMC is a more profitable semiconductor company than Intel

There is an interesting article on Seeking Alpha, “A More Profitable Semiconductor Company Than Intel”, and for a change the author does not PRETEND to know semiconductor technology. Refreshing! Personally I think the stock market is a racket where insiders profit at the expense of the masses. But if you are going to gamble you … Read More

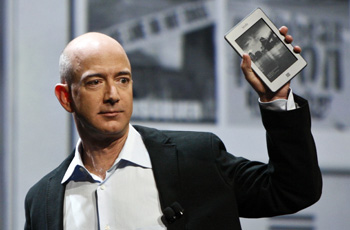

Apple Goes All Amazonian

In the world of Tech Goliaths, the seemingly low tech, not for profit Amazon continues to amaze investors with a high and rising stock price. More so than Google, Amazon is considered to have retail all wrapped up with the end game being sky-high warehouses and continuous truck rolls up and down our scenic neighborhoods. Walmart … Read More

From Layout Sign-off to RTL Sign-off

This week, I had a nice opportunity meeting Charu Puri, Corporate Marketing and Sushil Gupta, V.P. & Managing Director at Atrenta, Noida. Well, I know Sushil since 1990s; in fact, he was my manager at one point of time during my job earlier than Cadence. He leads this large R&D development centre, consisting about 200 people… Read More

TSMC Q2 Results: Up 17%; 20nm and 16nm on track

TSMC announced their Q2 financial results yesterday. Revenue was $5.2B (at the high end of guidance) with net income of $1.6B. This is up 17.4% on Q1 and up 21.6% year-to-year. Gross margin is up too, at 49% which is up 3.2 points on Q1 and 0.3 points year-to-year. As usual the financial results are not directly that interesting since… Read More

The Semiconductor IDM Business Model is Dead!

While this was not specifically stated, it was certainly implied during the sessions I attended at SEMICON West this week: The traditional semiconductor business model (IDM) is coming to an end. Starting with the keynote: Foundry-driven Innovation in the Mobility Era,cost was the common theme in any discussion involving mobile… Read More

The Future of Mobile Semiconductor Devices

During my trip to Taiwan I hopped on over to Hong Kong for a speaking engagement. One of the things I do as an “Internationally Recognized Industry Expert” is help the financial world understand the semiconductor landscape as it pertains to SoCs and mobile devices. Usually I do this over the phone or in writing but I prefer to do it in… Read More

What is inside the iPhone5s? Samsung or TSMC?

As a semiconductor professional and an Apple customer I’m very interested to see what is inside the iPhone5s. Rumors are spreading, photos are leaking, creating a nice build up to the next release of the mobile device that changed the world.

Honestly, last year I was a bit disappointed with the iPhone5. Inside is the A6 SoC which uses… Read More