In early April, Gabriele Saucier kicked off Design & Reuse’s IPSoC Silicon Valley 2021 Conference. IPSoC conference as the name suggests is dedicated to semiconductor intellectual property (IP) and IP-based electronic systems. There were a number of excellent presentations at the conference. The presentations had been… Read More

Tag: throughput

Hogan Fireside Chat with Paul Cunningham at ESDA

If you’re in verification and you don’t know who Paul Cunningham is, this is a guy you need to have on your radar. Paul has risen through the Cadence ranks fast, first in synthesis and now running the verification group, responsible for about a third of Cadence revenue and a hefty percentage of verification tooling in the semiconductor… Read More

Arm Deliver Their Next Step in Infrastructure

Arm announced their Neoverse plans not long ago at TechCon 2018. Neoverse is a brand, launched by Arm, to provide the foundations for cloud to edge infrastructure in support of their vision of a trillion edge devices. To a cynic this might sound like marketing hype. Sure, they’re widely used in communications infrastructure and… Read More

4 goals of memory resource planning in SoCs

The classical problem every MBA student studies is manufacturing resource planning (MRP II). It quickly illustrates that at the system level, good throughput is not necessarily the result of combining fast individual tasks when shared bottlenecks and order dependency are involved. Modern SoC architecture, particularly … Read More

How to handle petabyte-scale traffic growth?

If you search the web for IP traffic growth, you will find many graphics, but the common result is that IP traffic is growing with high CAGR for many years and will again continue to grow with such high CAGR for the next five years. For example the global mobile data traffic is expected to grow with 53% CAGR 2015-2020… even if the smartphone… Read More

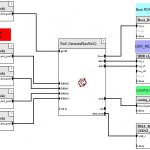

Taming The Interconnect In Real World For SoCs

Interconnect plays a significant role in the semiconductor design of a SoC; if not architected and handled well, it can lead to an overdesigned SoC impacting on its power, performance and area. Since a SoC generally contains multiple IPs requiring different data paths to satisfy varying latency and performance cycles, it has … Read More