You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

Did you know that an S-class Mercedes Benz can use 100 microprocessor-based electronic control units (ECUs) networking throughout the vehicle that run 20-100 million lines of code (Source: IEEE)?

2014 Mercedes-Benz CLA

Here’s a quick list of all the places that you will find software controlling hardware in an automobile:… Read More

Almost without exception these days, semiconductor products face strict power and thermal budgets. Of course there are many issues with dynamic power but one big area that has been getting increasingly problematic is static power. For various technical reasons we can no longer reduce the voltage as much as we would like from one… Read More

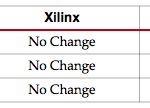

Most EDA start-up companies have a narrow product focus to complement existing tool flows, however Invarian is taking a much bolder approach by offering tools for:

- Power analysis

- Thermal analysis

- EM / IR analysis

- 3D Thermal analysis

…

Read More

I went to some of the JEDEC mobile conference a couple of weeks ago. The opening keynote was by Richard Wietfeld of Qualcomm called The Need for Speed.

He emphasized that smartphones are really setting the pace these days in all things mobile and internet. Over 1/3 of access is on smartphones now. Over 4/5 of searches on smartphones… Read More

Late in January it is DesignCon at the Santa Clara convention center from January 28th-31st. Details are here.

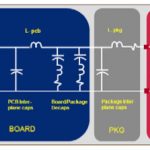

On Tuesday from 11.05 to 11.45 Apache and Ansys will be presenting on Thermal Co-analysis of 3D IC/packages/system. This is being presented by a whole team of people: Stephen Pan, senior product specialist at ANSYS; Norman… Read More

Increasingly the challenge with SoCs, especially for mobile, is not getting the performance high enough but doing so in a power-efficient manner. Handheld devices running multiple apps need high-speed processors that consume extremely low levels of power both in operating and standby modes. In the server farm, the limit is … Read More

Matt Elmore of ANSYS/Apache has an interesting blog posting about thermal analysis in 3D integrated circuits. With both technical and economic challenges at process nodes as we push below 28nm, increasingly product groups are looking towards through-silicon-via (TSV) based approaches as a way of keeping Moore’s law… Read More

For many, maybe most, big designs, Apache’s RedHawk is the signoff tool for analyzing issues around power: electromigration, power supply droop, noise, transients and so on. But the latest designs have some issues: they are enormous (so you can’t just analyze them naively any more than you can run a Spice simulation… Read More