We live in an exploding AI world, and this has put pressure on foundries to deliver new products faster than ever before. Any help to accelerate the semiconductor R&D goes a long way to make the life of Fab engineers easier. EDA tools in the TCAD (Technology Computer Aided Design) category are critical for TCAD engineers to accelerating… Read More

Tag: tcad

ASU Silvaco Device TCAD Workshop: From Fundamentals to Applications

The ASU-Silvaco Device Technology Computer-Aided Design Workshop is a pivotal educational and professional development event designed to bridge the gap between theoretical semiconductor physics and practical device engineering. Hosted by Arizona State University in collaboration with Silvaco, a leading provider of … Read More

Simulating Gate-All-Around (GAA) Devices at the Atomic Level

Transistor fabrication has spanned the gamut from planar devices o FinFET to Gate-All-Around (GAA) as silicon dimensions have decreased in the quest for higher density, faster speeds and lower power. Process development engineers use powerful simulation tools to predict and even optimize transistor performance for GAA devices.… Read More

Silvaco’s Diffusion of Innovation: Ecosystem Investments Driving Semiconductor Advancements

In Silvaco’s June 2025 Tech Talk, “The Diffusion of Innovation: Investing in the Ecosystem Expansion,” Chief Revenue Officer Ian Chen outlined how strategic partnerships accelerate R&D in semiconductor design and digital twin modeling. As a leading provider of TCAD, EDA software, and SIP solutions,… Read More

Silvaco at the 2025 Design Automation Conference #62DAC

Please join us at the Design Automation Conference 2025 where we will highlight the company’s wide range of EDA products and semiconductor IP targeting, Power Devices, Automotive, Memory, Displays, HPC, 5G / 6G, and IoT applications.

When: June 23 – 25, 2025, Exhibit Hours: 10:00 AM PDT – 6:00 PM PDT

Where: Moscone Center West,… Read More

TCAD for 3D Silicon Simulation

Semiconductor fabs aim to have high yields and provide processes that attract design firms and win new design starts, but how does a fab deliver their process nodes in a timely manner without having to run lots of expensive silicon through the line? This is where simulation and TCAD tools come into play, and to learn more about this… Read More

Intel Foundry Delivers!

Now that the dust has settled, I will give you my take on the Intel Foundry event. Some might call me a semiconductor event critic as I have attended hundreds of them over the last 40 years starting with the Design Automation Conference in 1984. Foundry events are my favorite because they really are the pulse of the semiconductor industry,… Read More

Understanding Sheath Behavior Key to Plasma Etch

Readers of SemiWiki will be well aware of the challenges the industry has faced in photolithography in moving to new nodes, which drove the development of new EUV light sources as well as new masking techniques. Plasma etching is another key step in chip manufacturing that has also seen new challenges in the development of new sub-10nm… Read More

SISPAD – Cost Simulations to Enable PPAC Aware Technology Development

I was invited to give a plenary address at the SISPAD conference in September 2021. For anyone not familiar with SISPAD it is a premiere TCAD conference. This year for the first time SISPAD wanted to address cost and my talk was “Cost Simulations to Enable PPAC Aware Technology Development”.

For many years the standard in technology… Read More

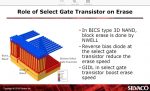

Webinar on coping with the complexities of 3D NAND design

In order to beat Moore’s Law NAND Flash memories have moved from a planar topology to 3D construction. This allows for increased memory sized in much the same way a multistory building provides more building square footage on the same size building lot. Just like in building construction, adding a third dimension to the mix increases… Read More