You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

In the traditional sense “Shift Left” is the process of making things simpler in an effort to make things faster. Shift Left was the theme of theDVCon keynote last week delivered by Synopsys co-founder and co-CEO Aart de Geus which is right on topic when it comes to modern semiconductor design and manufacturing, absolutely.

KEYNOTE:… Read More

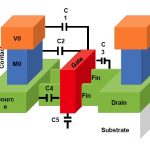

We read about FinFET technology in the semiconductor press daily now, thanks to Intel introducing their TriGate transistors starting in 2011 and creating a race with foundries and IDMs to switch from planar CMOS nodes. To get some perspective about the progress of FinFET IP and EDA tools I spoke with two experts from Synopsys, Swami… Read More

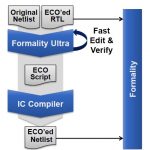

Your latest SoC has just begun the tape-out process and then marketing comes back with a small update to the specification to make your design more competitive, or maybe your regression tests just found a minor bug in a single IP block that needs to be fixed. Should you go back in your design flow, change the RTL source code and then completely… Read More

Synopsys announced their results yesterday. Their 2014 already ended, this is the end of their fiscal first quarter. On the call were Aart, one of Synopsys’s two co-CEOs, the other being Chi-Foon Chan; and Trac Pham, the new CFO on his first earnings call.

Synopsys’s results were good. A quick look at the results. Revenue was $542M… Read More

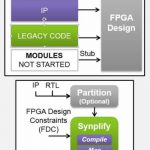

One of the recurring themes I see here in the pages of SemiWiki and elsewhere is this pitched, bordering on religious battle between Altera and Xilinx. Just because both are FPGA technologies, the tendency is to put them in the same bucket, drawing direct comparisons between them. Some folks say there is no comparison; Xilinx has… Read More

For about 5 years now Synopsys has held an HSPICE SIG event in conjunction with DesignCon. It features a small vendor faire with companies that partner with Synopsys on HSPICE flows. They also have a dinner with industry/customer speakers and provide an update on HSPICE development. Lastly there is a Q&A where customers get… Read More

When I hear the phrase Static Timing Analysis (STA) the first EDA tool that comes to mind is PrimeTimefrom Synopsys, and this type of tool is essential to reaching timing closure for digital designs by identifying paths that are limiting chip performance. Sunil Walia, PrimeTime ADV marketing lead spoke with me by phone on Thursday… Read More

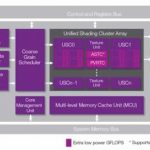

We have been hearing for some time about the Synopsys HAPS-70 and how they have co-created the hardware and software architecture for FPGA-based prototyping with their customers. Now, we see details published by Synopsys on how they collaborated with Imagination on the design of the PowerVR Series6XT GPU.

The first thing to come… Read More

This news in May 2014 that Samsung had licensed FD-SOI Technology from ST-Microelectronics was really amazing, as most of the industry was expecting this kind of agreement, but not with the #2 SC Company. But since May 2014 the news flow has been quite reduced, we can imagine that both SC companies had a lot work to do for transforming… Read More

With growing SoC size, complexity, software and hardware content in it and shrinking time-to-market, the SoC design completion in time has become increasingly dependent on IP which need to be sourced (internally or externally), customized according to the design need and integrated together into the SoC. While IP providers… Read More