I spoke with Aart before his SNUG keynote and found him to be very relaxed and upbeat about EDA and our future prospects which reminded me of my first ever (cringe-worthy) blog, “EDA is Dead”. Now, eight years later, we have what Aart calls “EDA Fusion” to thank for the reemergence of EDA as a semiconductor superpower, absolutely.… Read More

Tag: synopsys

Synopsys and PhoeniX Demo Photonic IC Flow Using AIM PDK at OFC

Synopsys has long been known for its leading position in the digital logic synthesis world. More recently however, the company started delving into the world of photonic integrated circuit (PIC) design. Synopsys started down this path from the system level with a 2010 acquisition of Optical Research Associates and their CODE… Read More

CEO Interview: Srinath Anantharaman of ClioSoft

It will soon be 20 years since ClioSoft started its journey of selling design management software for the semiconductor industry. It was a slow start considering that designs were relatively small and only digital front-end designers had begun to realize the importance of version control and design management. With open source… Read More

Using HSPICE StatEye to Tackle DDR4 Rail Jitter

The world is a risky place, according to Scott Wedge, Principal R&D Engineer at Synopsys, who presented at the Synopsys HSPICE SIG on Feb 2[SUP]nd[/SUP] in Santa Clara. Indeed, the world circuit designers face can be uncertain. Dealing with risk and departure from ideal was a main theme in the fascinating talks at this dinner… Read More

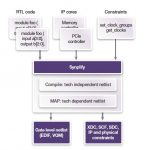

FPGA Design Gets Real

FPGA’s have become an important part of system design. It’s a far cry from how FPGA’s started out – as glue logic between discrete logic devices in the early days of electronic design. Modern day FPGA’s are practically SOC’s in their own right. Frequently they come with embedded processor cores, sophisticated IO cells, DSP,… Read More

SPIE Advanced Lithography and Synopsys!

SPIE is the premier event for lithography held in Silicon Valley and again Scotten Jones and I will be attending. EUV is generally the star of the show and this year will be no different now that TSMC has committed to EUV production in 2019.

Last year at SPIE, TSMC presented the history of EUV development from the beginning in 1985 as … Read More

Four Steps for Logic Synthesis in FPGA Designs

I remember meeting Ken McElvain at Silicon Compilers for the first time back in the 1980’s, he was a gifted EDA tool developer that did a lot of coding including logic synthesis, a cycle-based simulator and ATPG. Mentor Graphics acquired Silicon Compilers with Ken included, and he continued to create another logic synthesis… Read More

Nvidia Drives into New Market with Deep Learning and the Drive PX 2

Nvidia has found that video games are the perfect metaphor for autonomous driving. To understand why this is so relevant you have to realize that the way self-driving cars see the world is through a virtual world created in real time inside the processors used for autonomous driving – very much like a video game. It’s a little bit like… Read More

Expert Interview: Rajeev Madhavan

This blog was originally posted on Paysa.com but since Rajeev Madhavan is one of our EDA Heroes I thought it was worth a re-post. In case you do not know Rajeev, he started his EDA career at Cadence then was co-founder and VP of Engineering at LogicVision (acquired by Mentor). Next he was Founder, President, and Chairman of Ambit Design… Read More

ATPG, Automotive and 7nm FinFET

The state of Texas hosted two or our industry’s big technical conferences and trade shows this year: DAC and ITC (International Test Conference). IC designers know about DAC in Austin, and test engineers know about ITC in Dallas. I travelled to Austin to cover DAC this past summer, and I was able to connect with Robert Ruiz … Read More