Power devices have historically been made from silicon (Si), which has reached the limit of electric power loss reduction. With the superior physical and electrical properties of silicon carbide (SiC), we can expect to see a significant expansion in the amount of electric power conversion of electrical equipment as well as reduced… Read More

Tag: spice

Expert Tool to View and Debug Design Issues at Spice Level

Spice view of a design, block or fragment of the design is probably the lowest level of functional description of a circuit in terms of transistors, resistors, capacitors, interconnect and so on, which in several ways acts as an ultimate proof of pudding for any semiconductor design before manufacturing. However, it’s generally… Read More

A Comprehensive Power Analysis Solution for SoC+Package

Since power has become a critical factor in semiconductor chip design, the stress is towards decreasing supply voltage to reduce power consumption. However, the threshold voltage to switch devices cannot go down beyond a certain limit and these results in an extremely narrow margin for noise between the two. And that gets further… Read More

Design & EDA Collaboration Advances Mixed-Signal Verification through VCS AMS

Last week it was a rare opportunity for me to attend a webinar where an SoC design house, a leading IP provider and a leading EDA tool provider joined together to present on how the tool capabilities are being used for advanced mixed-signal simulation of large designs, faster with accuracy. It’s always been a struggle to combine design… Read More

Analog Model Equivalence Checking Accelerates SoC Verification

In the race to reduce verification time for ever growing sizes of SoCs, various techniques are being adopted at different levels in the design chain, functional verification being of utmost priority. In an analog-digital mixed design, which is the case with most of the SoCs, the Spice simulation of analog components is the limiting… Read More

Analog FastSPICE Update at DAC

Tuesday night over dinner at DAC I was able to chat with Ravi Subramanian, CEO of Berkeley DA, recently acquired by Mentor Graphics back on March 21st. This acquisition provided Mentor with an Analog FastSPICE circuit simulator to round out its collection of simulators.… Read More

Active Power Management in UPF Using SPICE, VHDL-AMS or Verilog-AMS

My former co-worker, Kenneth Bakalar at Mentor Graphics is an expert in AMS modeling languages and UPFmethodology, so he recently teamed up with Eric Jeandeau to author an interesting white paper: Interpreting UPF for a Mixed-Signal Design Under Test. This white paper is based on a presentation made at DVCon earlier this year.… Read More

Concept Engineering Showcases Effective SoC Debugging Techniques

In a complex environment of semiconductor design where an SoC can have several millions of gates and multiple number of IPs at different levels of abstractions from different sources integrated together, it becomes really difficult to understand and debug the overall SoC design. Of course, along with the SoC integration, optimization… Read More

Teach Yourself Silvaco

In the dim and distant past, if you wanted to learn how to use a particular EDA tool then you would go on a training course. This would often be multiple days and often a significant dollar investment too. For most EDA companies, that option still exists and the big 3 have quite extensive training catalogs.

But nowadays it is often easier… Read More

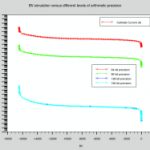

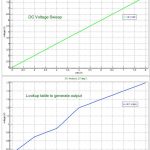

Analog and Full Chip Simulation at Micron

IDM companies like Micronuse SPICE circuit simulators during the design phase in order to predict timing, currents and power on their custom IC chip designs at the transistor level. A senior memory design engineer at Micron named Raed Sabbahtalked today at a webinarabout how the embedded solutions group uses the FineSimcircuit… Read More