I started out my engineering career by doing transistor-level circuit design and we used a proprietary SPICE circuit simulator. One thing that I quickly realized was that the accuracy of my circuit simulations depended entirely on the model files and parasitics. Here we are 40 years later and the accuracy of SPICE circuit simulations… Read More

Tag: spice

SPICE Model Generation by Machine Learning

It was 1988 when I got into SPICE (Simulation Program with Integrated Circuit Emphasis)while I was characterizing a 1.5 μm Standard cell library developed by students at my Alma-Mata Furtwangen University in Germany. My professor Dr. Nielinger was not only my advisor he also wrote the first SPICE bible in German language. At that… Read More

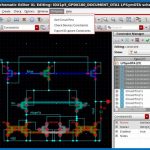

The Intention View: Disruptive Innovation for Analog Design

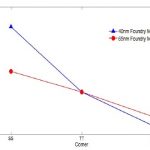

Intento Design builds responsive analog EDA. The ID-Xplore tool is used for analog design acceleration and technology porting at the functional level, helping companies move analog IP quickly between technology nodes and across business units. The Intention view is a simple, elegant, and powerful concept that gives the speed… Read More

EDA Machine Learning from the Experts!

Traditionally, EDA has been a brute force methodology where we buy more software licenses and more CPUs and keep running endless jobs to keep up with the increasing design and process complexities. SPICE simulation for example; when I meet chip designers (which I do quite frequently) I ask them how many simulations they do for a … Read More

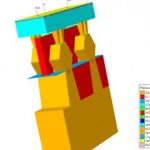

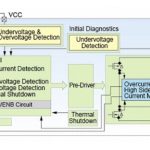

Electrothermal Analysis of an IC for Automotive Use

Automotive ICs have to operate in a very demanding environment in terms of both temperature and voltage ranges, along with the ability to withstand g-forces and be sealed from the elements. Not an easy design challenge. For many consumer ICs we see output drive currents on the IO pins measured in mA, however in automotive if you want… Read More

Webinar on TFT and FPD Design

I knew that the acronym for TFT meant Thin Film Transistors, but I hadn’t heard that FPD stands for Flat Panel Detectors. It turns out the FPD are solid-state sensors used in x-ray applications, similar in operation to image sensors for digital photography and video. I’ll be attending and blogging about what I learn… Read More

Analyzing All of those IC Parasitic Extraction Results

Back at DAC in 2011 I first started to hear about this EDA company named edXact that specialized in reducing and analyzing IC parasitic extraction results. So Silvaco acquired edXact and I wanted to get an update on what is new with their EDA tools that help help you to analyze and manage the massive amount of extracted RLC and even K … Read More

SPICE Model Generation using Machine Learning

AI and machine learning are two popular buzz words in the high-tech daily news, so you should be getting used to hearing about them by now. What I hadn’t realized was that EDA companies are starting to use machine learning techniques, and specifically targeted at the daunting and compute intensive task of creating SPICE models… Read More

CEO Interview: Rene Donkers of Fractal Technologies

Fractal is another one of those very successful emerging EDA companies that you don’t read a lot about, except on SemiWiki. Rene Donkers is co-founder and CEO of Fractal Technologies, a company addressing IP quality assurance. This is a niche in the SoC tooling market that deserves some justification. Why not use an IP as-is… Read More

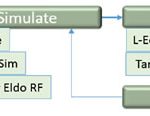

Can one flow bring four domains together?

IoT edge device design means four domains – MEMS, analog, digital, and RF – not only work together, but often live on the same die (or substrate in a 2.5D process) and are optimized for power and size. Getting these domains to work together effective calls for an enhanced flow.

Historically, these domains have not played together … Read More