In the current decade of SoCs, semiconductor design size and complexity has grown by unprecedented scale in terms of gate density, number of IPs, memory blocks, analog and digital content and so on; and yet expected to increase further by many folds. Given that level of design, it’s imperative that SoC verification challenge has… Read More

Tag: soc

Intel Quark awakening from stasis on a yet-to-be-named planet

We know the science fiction plot device from its numerous uses: in order to survive a journey of bazillions of miles across galaxies into the unknown future, astronauts are placed into cryogenic stasis. Literally frozen in time, the idea is they exit a lengthy suspension without aging, ready to go to work immediately on revival … Read More

Dual Advantage of Intelligent Power Integrity Analysis

Often it is considered safer to be pessimistic in estimating IR-drop to maintain power integrity of semiconductor designs; however that leads to the use of extra buffering and routing resources which may not be necessary. In modern high speed, high density SoCs having multiple blocks, memories, analog IPs with different functionalities… Read More

How Do You Verify a NoC?

Networks-on-chip (NoCs) are very configurable, arguably the most configurable piece of IP that you can put on a chip. The only thing that comes close are highly configurable extensible VLIW processors such as those from Tensilica (Cadence), ARC (Synopsys) and CEVA but Sonics would argue their NoCs are even more flexible. But … Read More

Wearables the Big Hit at CES

There were a number of trends discernible at CES this year, one of the big ones being wearables, especially in the medical and fitness areas. I wear a FitBit Flex and I have, but rarely wear, a Pebble Watch that links to my iPhone. I would say that at this point they are promising but are more gimmicks than truly useful. My Fitbit measures… Read More

NoC, NoC: Your Chip May Be Under Attack

SoCs face a lot of issues related to security and the Network-on-Chip (NoC) is in a good position to facilitate system-wide services. SoCs are now so complex that one of the challenges is to make sure that the chip does what it is meant to do and doesn’t do what it isn’t meant to do. Just as in software, security used to be … Read More

Cadence & ARM Optimize Complex SoC Performance

Now a day, a SoC can be highly complex, having 100s of IPs performing various functionalities along with multi-core CPUs on it. Managing power, performance and area of the overall semiconductor design in the SoC becomes an extremely challenging task. Even if the IPs and various design blocks are highly optimized within themselves,… Read More

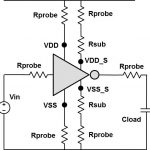

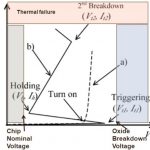

Full Chip ESD Sign-off – Necessary

As Moore’s law keeps going, semiconductor design density on a chip keeps increasing. The real concern today is that the shrinkage in technology node has rendered the small wire geometry and gate oxide thickness (although fine in all other perspectives) extremely vulnerable to ESD (Electrostatic Discharge) effects. More than… Read More

Debugging Complex Embedded System – How Easy?

In today’s world of semiconductor design with SoCs having complex IPs, hardware and software working together on a single chip, it’s hard to imagine a system without embedded software into it. But it is easy to guess how difficult it would be to test that hardware and software embedded system. And often there is limited window of … Read More

TSMC on Semiconductor IP Quality

It is important to note that the System On Chip (SoC) revolution that is currently driving mobile electronics has one very important enabling technology and that is Semiconductor Intellectual Property. Where would we be without the commercial IP market segment? Computers and phones would still be on our desks for one thing, and… Read More