Xilinx has delivered not only “the biggest FPGA on the planet”, but what it claims is currently the world’s largest integrated circuit: the Virtex UltraScale VU440, with 19 billion transistors fabbed in TSMC 20nm. The list of first customers to receive parts says a lot about the state of SoC design today, and the vital role FPGA-based… Read More

Tag: soc design

SoCs should invest in a strong cache position

Like most technology firms, Apple has been home to many successes, and some spectacular defeats. One failure was Project Aquarius. At the dawn of the RISC era, before ARM architecture was “discovered” in Cupertino, engineers were hunkered over a Cray X-MP/48. The objective was to design Apple’s own quad core RISC processor to … Read More

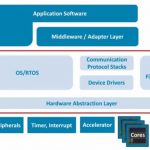

3 reasons to focus on hardware dependent software

Why is software for modern SoCs so blasted expensive to develop? One reason is more software is being developed at the kernel layer – hardware dependent software, or HdS. Application software often assumes the underlying hardware, operating system, communication stacks, and device drivers are stable. For HdS, this flawed assumption… Read More

CEVA creating a wearable IP platform

Processor and GPU cores usually get the limelight, driven by the ARM and Imagination machines occupying the center square of most SoC designs. CEVA has quietly been assembling DSP IP in most of the squares around the edge, and may have just reached critical mass for wearables and IoT devices.… Read More

A song of optimization and reuse

If you hang around engineers for any time at all, the word optimization is bound to come up. The very definition of engineer is to contrive or devise a solution. With that anointing, most engineers are beholden to the idea that their job is creating, synthesizing, and perfecting a solution specifically for the needs of a unique situation.… Read More

Show Me How To Get Better DRC and LVS Results For My SoC Design

Most IC engineers learn best by hands-on experience when another more experienced person can show us what to do. If you cannot find that experienced person, then the next best thing is a video from an expert. I was surprised to find out that video was so important today that the #2 most viewed web site on the Internet was www.youtube.com… Read More

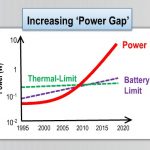

Early RTL Power Analysis and Reduction

Power analysis and reduction for SoC designs is a popular topic because of our consumer electronics dominated economy, and the need to operate devices on a battery source for the maximum time before a recharge. Just from my desk I can see multiple battery-powered devices: Laptop, tablet, smart phone, e-book reader, bluetooth … Read More

Rise of the cloudphone?

We’re all quite twitterpated with the smartphone. Admittedly, it has taken much of the world by storm, and dominates EDA discussion because of the complex SoCs inside. Feature phones have repeatedly been declared dead, or at least disinteresting, but the numbers tell a different story.

While Europe and the US enjoy much higher… Read More

ISO 26262 driving away from mobile SoCs

Connected cars may be starting to resemble overgrown phones in many ways, but there are critical differences now leading processor teams in a different direction away from the ubiquitous mobile SoC architecture – in turn causing designers to reevaluate interconnect strategies.

The modern car has evolved into a microcontroller… Read More

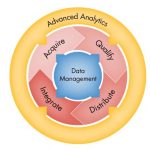

Webinar: IP Lifecycle Management: What is it, what problems does it solve?

SoC’s are now dominated by IP blocks sourced either from 3rd parties or internal design teams. This means that IP is now critical to the success of the SoC, yet it is part of the design that teams have the least control over, or visibility into. Most design teams utilize at best ad-hoc methods to manage this IP, and the few that utilize… Read More