You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

The engineering team for the design and analysis of a complex system consists of a diverse set of skills — with the increasing emphasis on both high-speed interface design and multi-domain power management, a critical constituent of the team is the group of signal integrity (SI) and power integrity (PI) engineers.

The training… Read More

It’s hard to believe but this is DesignCon #22 and being a Silicon Valley conference I have attended my fair share of them. This year it seems like high speed communications will take the lead followed by the latest on PCB design tools, power and signal integrity, jitter and crosstalk, test and measurement tools, parallel … Read More

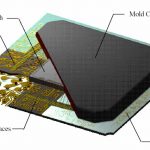

2015 will be remembered as the year when chip-package-system (CPS) physical co-design and electrical/thermal analysis methodologies took center stage.… Read More

As we move towards packing more and more functionalities and increasing densities of SoCs, the power, thermal and signal integrity issues keep on rising. 3D-IC is a great concept to stack multiple dies on top of each other vertically. While it brings lot of avenues to package dies with multiple functions together, it has challenges… Read More

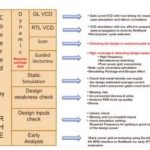

As power has become one of the most important criteria in semiconductor design today, I was wondering whether there is a standard set for the power verification for an overall chip. We do have formats evolved like CPF and UPF and there are tools available to check power and signal integrity (SI), however I don’t see a standard objective… Read More

When Cadence acquired Sigrity in 2012, two motives were involved: get more competitive in state of the art signal integrity analysis, and grab a foothold into the other vendor’s PCB flows in an area that is developing as a real sore spot for digital designers.

Just as the days where PCB tape-out meant actually using tape are over, … Read More

In July Cadence acquired Sigrity, one of the leaders in PCB and IC packaging analysis. Until a decade ago, signal integrity and power analysis was something that only IC designers needed to worry about. For all except the highest performance boards, relatively simple tools were sufficient. Provided you hooked up the pins on all… Read More

Matt Elmore has a two-part blog about the growing complexity of signal integrity analysis, both on the chip itself and the increasingly complex analysis required to make sure that signals (and power) get in and out of the chip from the board cleanly, especially to memory, which requires simultaneous analysis of chip-package-system… Read More

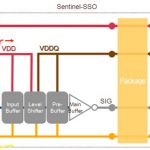

Chips, packages and circuit boards (systems, hence CPS) used to be three separate domains with their own tools that barely interacted at all. If you were lucky, reassigning a pin on a package wouldn’t have to be done manually in all 3 places. But now, from a signal integrity, noise, power point of view these three domains must… Read More