Complexity and density conspire to make power delivery very difficult for advanced SoCs. Signal integrity, power integrity, reliability and heat can seem to present unsolvable problems when it comes to efficient power management. There is just not enough room to get it all done with the routing layers available on the top side… Read More

Tag: signal integrity

Podcast EP168: The Extreme View of Meeting Signal Integrity Challenges at Wild River Technology with Al Neves

Dan is joined by Al Neves, Founder and Chief Technology Officer at Wild River Technology. Al has 30 years of experience in design and application development for semiconductor products and capital equipment focused on jitter and signal integrity. He is involved with the signal integrity community as a consultant, high-speed… Read More

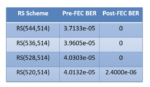

Mitigating the Effects of DFE Error Propagation on High-Speed SerDes Links

As digital transmission speeds increase, designers use various techniques to improve the signal-to-noise ratio at the receiver output. One such technique is the Decision Feedback Equalizer (DFE) scheme, commonly used in high-speed Serializer-Deserializer (SerDes) circuits to mitigate the effects of channel noise and … Read More

A MasterClass in Signal Path Design with Samtec’s Scott McMorrow

We all know signal integrity and power integrity are becoming more important for advanced design. Like package engineering, the obscure and highly technical art of SI/PI optimization has taken center stage in the design process. And the folks who command expertise in these areas have become the rock stars of the design team. I … Read More

Enabling Next Generation Silicon In Package Products

In early April, Gabriele Saucier kicked off Design & Reuse’s IPSoC Silicon Valley 2021 Conference. IPSoC conference as the name suggests is dedicated to semiconductor intellectual property (IP) and IP-based electronic systems. There were a number of excellent presentations at the conference. The presentations had been… Read More

Maximizing ASIC Performance through Post-GDSII Backend Services

ASICs by definition are designed to meet the respective applications’ requirements. ASIC engineers deploy various design techniques to maximize performance, minimize power and reduce chip size. But is there more that can be done after the GDSII is taped out? A recent press release from Alchip Technology dated Feb 4, 2021 claims… Read More

Samtec Lets You Learn from Home with a Great Webinar Lineup

Work from home (WFH) has become a normal occurrence this past year. “Do you work from home?” “Of course, where else?” Samtec is taking the whole work from home thing up a notch with a new webinar lineup for 2021. Back by popular demand, they are launching a new series of educational webinars. Started last year, the gEEk SpEEk Webinar… Read More

Bridging the Gap Between Design and Analysis

At the recent DesignCon 2020 in Santa Clara, Cadence introduced a new product, Sigrity Aurora. You won’t find a press release about this announcement. Rather, Brad Griffin, product management group director at Cadence, presented Sigrity Aurora in the theater at the Cadence booth. This one caught my eye and deserves some discussion.… Read More

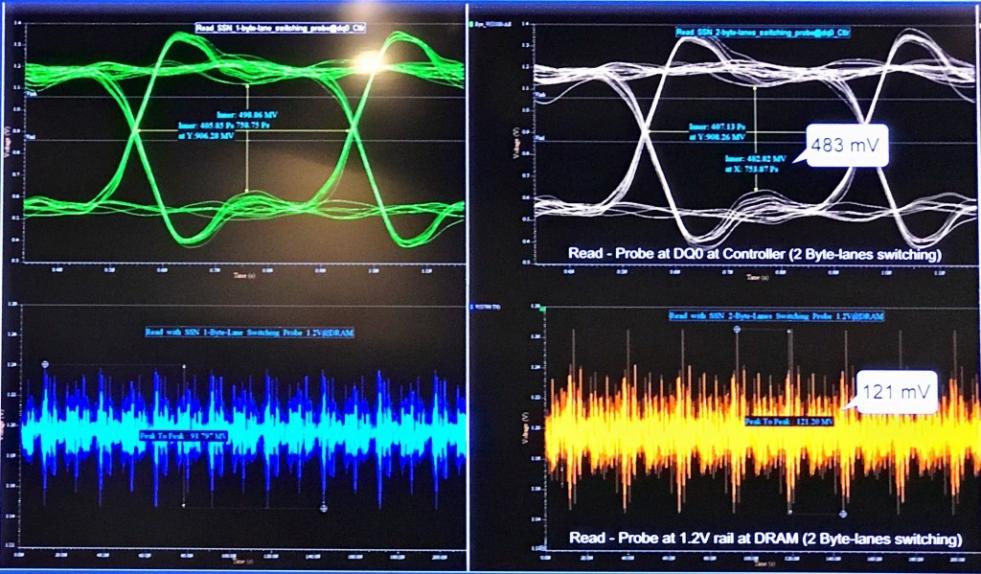

Mentor Automating Design Compliance with Power-Aware Simulation HyperLynx and Xpedition Flow

High-speed design requires addressing signal integrity (SI) and power integrity (PI) challenges. Power integrity has a frequency component. The Power Distribution Network (PDN) in designs has 2 different purposes: providing power to the chip, and acting as a power plane reference for transmission-line like propagating … Read More

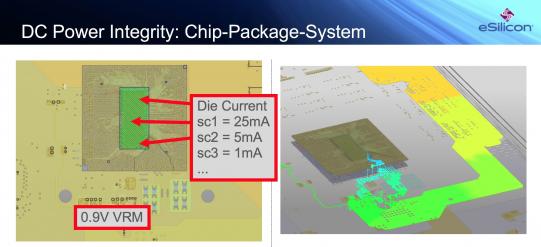

Chip, Package, System Analysis – A User View

While I missed ANSYS (and indeed everyone else) at DAC this year, I was able to attend the ANSYS Innovation Conference last week at the Santa Clara Convention Center. My primary purpose for being there was to listen to a talk by eSilicon which I’ll get to shortly, but before that I sat through a very interesting presentation on the growing… Read More