Wednesday, March 11 – 8:00 AM Pacific

Design and verification teams consistently tell us that compute subsystems require software bring up much earlier than ever before. They need UEFI and Linux to run in simulation, they need protocol accuracy from day one, and they need a predictable path to signoff while integration … Read More

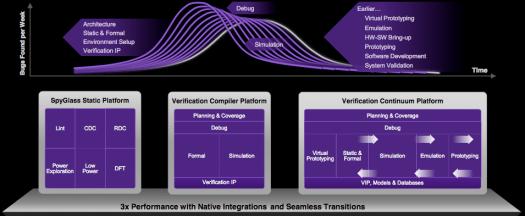

At the heart of the shift-left strategy is the goal of moving traditionally late-stage tasks—such as software development, validation, and optimization—earlier in the design process. This proactive approach allows teams to identify and resolve issues before they escalate, reducing costly rework and shortening the overall… Read More

In today’s rapidly evolving semiconductor industry, the design and integration of intellectual property (IP) play a pivotal role in achieving competitive advantage and market success. Whether sourced from commercial IP providers or developed in-house, ensuring that IP designs are compliant with signoff requirements… Read More

According to McKinsey & Company, a digital twin is a digital representation of a physical object, person, or process, contextualized in a digital version of its environment. Digital twins can help an organization simulate real situations and their outcomes, ultimately allowing it to make better decisions. Anyone… Read More

Advanced process nodes create challenges for EDA both in handling ever larger designs and increasing design process complexity.

Shift-left design methodologies for design cycle time compression are one response to this. And this has also forced some rethinking about how to build and optimize design tools and flows.

SemiWiki… Read More

When discussing FPGA-based prototyping, we often focus on how to pour IP from a formative SoC design into one or more FPGAs so it can be explored and verified before heading off to a foundry where design mistakes get expensive. There’s also the software development use case, jumpstarting coding for the SoC before silicon … Read More

Everyone saw Shift Left, the EDA blockbuster. Digital logic design, with perfect 1s and 0s simulated through perfect switches, shifted into a higher gear. But the dark arts – RF systems, power supplies, and high-speed digital – didn’t shift smoothly. What do these practitioners need in EDA to see more benefits from shift left? … Read More

Ever since the cost of development started growing exponentially, engineering teams have been deploying a shift-left strategy to software development and system verification. While this has helped contain cost and accelerated product development schedules, a shift-left strategy is not without challenges. A virtual platform… Read More

Shift-left, why?

Shift-left testing is an approach to software and system testing which is performed earlier in the lifecycle (that is, moved left on the project timeline). It is the first half of the “Test early and often” maxim that was coined by Larry Smith in 2001.

It’s now an established idea, much talked about … Read More

Unless you have been living in a cave for the last several years, by now you know that “Shift Left” is a big priority in product design and delivery, and particularly in verification. Within the semiconductor industry I believe Intel coined this term as early as 2002, though it seems now to be popular throughout all forms of technology… Read More