One of the places you will be able to find me at the Design Automation Conference (DAC) is on the speaker panel for a Monday Tutorial – Winning in Monte Carlo: Managing Simulations Under Variability and Reliability. Having worked closely with TSMC, GLOBALFOUNDRIES, Solido Design Automation, and some of the top fabless semiconductor… Read More

Tag: semiconductors

SoC Optimization Using FPGA Prototyping

As an engineer I learn new concepts best by seeing a demonstration, in this case it was a demo of how to optimize SoC performance by using an ASIC prototyping debug process. SoC designers that use FPGAs to prototype their new ASIC often encounter debug issues, like:

- Limited observability of internal nets required for debug, maybe

Atrenta CEO on RTL Signoff

Most EDA companies sell tools into the main chip design and implementation flow such as simulation, synthesis, place & route, custom design and mask data prep. Atrenta is different. Nothing the company sells is in this main design flow. Instead, Atrenta focuses on pre-synthesis design analysis and optimization. Everything… Read More

Chip and I/O Modeling for System-level Power Noise Analysis and Optimization

Cornelia Golovanovworks at LSI Corp in Pennsylvania and is an EMI expert that provides EDA tool and methodology advise to design groups. She earned a PhD in microelectronics and radioelectricity from the Institut national polytechnique de Grenoble, and joined Lucent out of school 12 years ago. We had a chance to talk by phone about… Read More

UVM/SystemVerilog: Verification and Debugging

At DAC in just three weeks you can learn about which EDA vendors are supporting the latest UVM 1.1d (Universal Verification Methodology) standard as defined by Accellera. One of those EDA vendors is Aldec, and they have a 45 minute technical session that you can register for online. Space will fill up quickly, so get signed up sooner… Read More

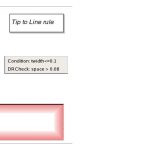

iDRM Brings Design Rules to Life!

Much awaited, automatic tool for DRM (Design Rule Manual) and DRC (Design Rule Check) deck creation is here now! I am particularly excited to know about this because I had been hearing for its need (in different context) from the designers with whom I was working to improve their design productivity through the use of our EDA tools… Read More

Prototyping Over 100 Million ASIC Gates Capacity

Most SoCs today are being prototyped in FPGA hardware before committing to costly IC fabrication. You could just design and build your own FPGA prototyping system, or instead choose something off the shelf and then concentrate on your core competence of SoC design.

Thanks to the FPGA vendors like Xilinx we now have FGPA prototyping… Read More

Forte CEO on Design and Verification Complexity

Sean Dart’s first DAC (Las Vegas) was as a customer in 1989. Designs were hitting 15,000 gates back then so he was looking for better schematic editors and simulators for gate level design. Fast forward 25 years and Sean’s customers are doing 15,000,000 gate subsystems and that number is growing steadily every year.… Read More

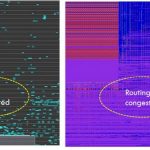

Modern SoC designs require a placement- and routing-aware ECO solution to close timing

As an applications engineer for over 15 years supporting physical design tools that enable implementation closure, I have seen the complexity of timing closure grow continuously from one process node to the next. At 28nm, the number of scenarios for timing sign-off has increased to the extent that is way beyond the number that … Read More

Improving Design Practices for an Image Sensor IDM

With nearly twenty five years in business, Tanner EDA Application Engineers have seen a wide range of support requests. One consistent topic area is around design data management and design reuse. In one recent instance, our customer, an IDM who produces imaging sensors for infrared vision systems, called on Tanners AE team for… Read More