Mobile is one of the biggest markets for semiconductor, especially if you count not just mobile handsets but also the base-station infrastructure. No technology has ever been adopted so fast and so completely. There are approximately the same number of mobile phone accounts as there are people in the world. A few people have more… Read More

Tag: semiconductor

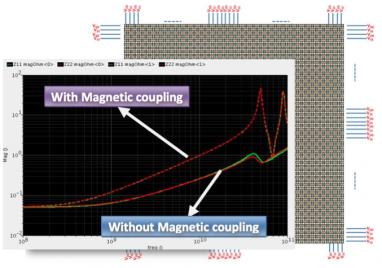

Power Integrity Challenges for High Speed and High Frequency Designs

There is an interesting discussion on the LinkedIn SoC Power Integrity Group in regards to the power integrity challenges for high speed and high frequency designs. More specifically, the additional attention an on-chip power delivery network (PDN) requires as the operating frequency of ICs and SoCs increases.

The PDN has to… Read More

Advanced Node Design Webinar Series

At advanced process nodes, variation and its effects on the design become a huge challenge. Join Cadence® Virtuoso® experts for a series of technical webinars on variation-aware design. Learn how to use advanced technologies and tools to analyze and understand the affects of variation. We’ll introduce you to the latest Virtuoso… Read More

A Brief History of Moore’s Law

I recently read a news article where the author referred to Moore’s Law as a ‘Law of Science discovered by an Intel engineer’. Readers of SemiWiki would call that Dilbertesque. Gordon Moore was Director of R&D at Fairchild Semiconductor in 1965 when he published his now-famous paper on integrated electronic… Read More

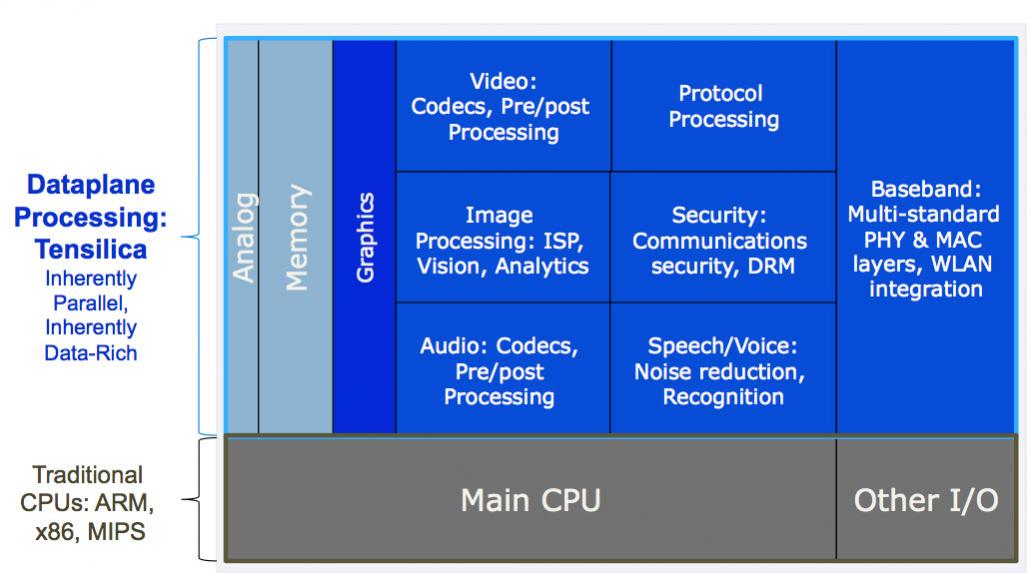

The Protocol Processing Dataplane

At the Linley processor conference this week, Chris Rowen, the CTO of Tensilica presented on the protocol processing dataplane. That sounds superficially like he is talking about networking but in fact true protocol processing is just part of adding powerful compute features to the dataplane. Other applications are video, … Read More

ARM in Networking/Communications

I was at the Linley Processor Conference yesterday. There are two of these each year, one focused on mobile and this one, focused on networking and communications (so routers, base-stations and the like). You probably know that ARM is pretty dominant in mobile handsets (and Intel is trying to get a toe-hold although I’m skeptical… Read More

Tensilica Ships 2 Billionth Core

It was in June of last year that Tensilica announced that they (or rather their licensees) had shipped one billion cores. Now they have just announced that they have shipped two billion cores. They are shipping at a run-rate of 800 million cores per year, which is 50% higher than June last year. If business continues to grow they will… Read More

ICCAD: 30 years

ICCAD is November 5th to 8th in the Hilton San Jose (downtown).

It is very off topic, but if you are British then November 5th is the rough equivalent of July 4th when there are fireworks displays all over the country. Britain is one of very few countries that transitioned from some sort of autocracy to a democracy without having a revolution.… Read More

Soft IP Quality Standards

As SoC design has transformed from being about writing RTL and more towards IP assembly, the issue of IP quality has become increasingly important. In 2011 TSMC and Atrenta launched the soft IP qualification program. Since then, 13 partners have joined the program.

IP quality is multi-faceted but at the most basic level, an IP block… Read More

Apache Dimensions of Electronic Design Seminars

Coming up are ANSYS/Apache seminars on Dimensions of Electronic Design. Watch the video where Arvind Shanmugavel gives some details about why you should attend. Probably most readers are in Silicon Valley, and the seminar here is on 18th at the Hyatt (next to Santa Clara convention center).

The seminars are free to qualified attendees.… Read More