David Avercrombie of Mentor won the award for the best tutorial at the 2012 TSMC OIP for his presentation, along with Peter Hsu of TSMC, on Finding and Fixing Double Patterning Errors in 20nm. The whole presentation along with the slides is now available online here. The first part of the presentation is an introduction to double … Read More

Tag: semiconductor

A Brief History of Apache Design

Apache Design Solutions was founded in 2001 by Andrew Yang and three researchers from HP Labs (Norman Chang, Shen Lin, Weize Xie). They realized that engineers striving to meet the goal of increased device miniaturization, as defined by Moore’s Law, would eventually hit stumbling blocks in their progress. The founding team believed… Read More

Is the RTL Design Flow Broken?

I’ve taught Verilog classes and used logic synthesis tools for ASIC and FPGA designs, so was interested to hear about Oasys Design Systems. I attended their webinar at 9AM today, so I’ll share what I learned about their approach to logical and physical synthesis. This approach competes with tools like Design Compiler… Read More

ESD Check Methodology

In Pune at the start of the month, Norman Chang, Ting-Sheng Ku, Jai Pollayil of Apache/Ansys and NVIDIA presented and ESD check methodologywith Fast Full-chip Static and Macro-level Dynamic Solutions . ESD stands for Elecro-Static Discharge and is basically injecting very high static voltages (think how your hand gets charged… Read More

Predictions are hard, especially about the future

I was asked to make some predictions about the EDA, semiconductor and electronic systems markets for 2013. I decided that it would be more fun to make some plausible predictions, some of which will be right, rather than go for anodyne predictions (“Cadence will acquire a couple of startups”) which are uninformative,… Read More

Reducing Dynamic and Static Power in Memories

Sequential approaches to power reduction work well on logic implemented using standard cells. But part of every SoC, sometimes a very large part, is taken up with embedded memories for which alternative approaches are required. Not only do these memories occupy up to half of the area they also account for as much as 75% of the power… Read More

Global Design Closure

Satish Soman, chief solutions architect at Atrenta, was invited to give a presentation on Global Design Closure at the VLSI India conference in Pune at the start of this month. He talked about the need to close the gap between the typical SoC development methodology and what happens in reality.

SoCs are really put together in two … Read More

Tech Forum, February 5, features 32/28-, 20-, 14-, and 10-nanometer processes

The Common Platform Alliance — IBM, Samsung Electronics, Co., Ltd., and GLOBALFOUNDRIES — continues to redefine the landscape of the semiconductor industry with its groundbreaking collaboration. Join us at our 2013 Common Platform Technology Forumon Tuesday, February 5, 2013 at the Santa Clara Convention Center as we showcase… Read More

HiFi Mini, Always Listening

Next week it is the Consumer Electronics Show (CES) in Las Vegas and so there are announcements around the areas where consumer overlaps with semiconductor, which these days is primarily mobile. Then in February in Barcelona is Mobile World Congress, which is even more focused on mobile. Expect more announcementst there.

Currently… Read More

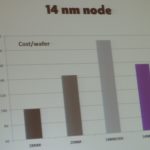

Wafer Costs: Out of Control or Not?

I didn’t attend the International Electronic Device Meeting (IEDM) earlier this month, but there have been a lot of reports on the inter webs especially about 20nm and 14nm processes. Some of this is really geeky stuff but I think that perhaps the most interesting thing I’ve read about is summarized in this chart:

This… Read More