You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

One of the nice things about being part of a website such as SemiWiki is that you get to see real-time trends and analytics. SemiWiki is built on top of a relational database with a full content manager and integrated analytics. It also allows us to see historical data that we can compare and contrast to what is happening today.

One of… Read More

When I was not messing around with FPGA Research and Development, or Algorithms, I was often called into the lab or field and presented this type of scenario… Most of the time, the fix was the same…

At least a few times a year, I’d get the call. Sometimes a panic in the voice, or sometimes defeat. And who wouldn’t be defeated? After… Read More

The theme of this year’s GSA Silicon Summit is More than Moore. This has become a sort of catchall phrase for technologies other than simply moving to the next process node. The summit is on April 18th at the computer history museum (1401 Shoreline Blvd). Registration takes place at 9am and the actual sessions start at 9.45am.… Read More

My background is IC design engineering, so it’s always a delight to talk with another engineer on their chip challenges. Today I spoke by phone with Sucharita Biswas, a Senior Hardware Engineer at Altera involved in IC test debug for FPGA devices.

… Read More

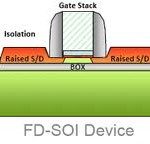

I recently spoke to Arvind Narayanan, Product Marketing Manager for Mentor’s place and route division about emerging technology. This of course led to FinFETS, FDSOI, performance, power, and cost-benefit. The battle between FDSOI and FinFETs, said Narayanan, is going to be something to watch.

Both FDSOI and FinFET technologies… Read More

RTL Restructuringby Daniel Payne on 04-04-2013 at 2:34 pmCategories: EDA

Hierarchical IC design has been around since the dawn of electronics, and every SoC design today will use hierarchy for both the physical and logical descriptions. During the physical implementation of an SoC you will likely run into EDA tool limits that require a re-structure of the hierarchy. This re-partitioning will cause… Read More

UBM’s EETimes and EDN today announced Kathryn Kranen as the lifetime achievement award winner for this years ACE awards program. Kathryn, of course, is the CEO of Jasper (and is also currently the chairman of EDAC). Past winners exemplify the prestige and significance of the award. Since 2005 the award was given to Gordon… Read More

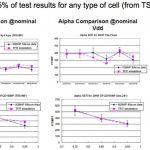

I blogged last month about single event effects (SEE) where a semiconductor chip behaves incorrectly due to being hit by an ion or a neutron. Since we live on a radioactive planet and are bombarded by cosmic rays from space, this is a real problem, and it is getting worse at each process node. But just how big of a problem is it?

TFIT is … Read More

This year’s recipient of the Kaufman Award is Dr Chenming Hu. I can’t think of a more deserving recipient. He is the father of the FinFET transistor which is clearly the most revolutionary thing to come along in semiconductor for a long time. Of course he wasn’t working alone but he was the leader of the team at UC… Read More

Given the compressed time between 20nm and 16nm, twelve months versus the industry average twenty four months, it is time to start talking about 10nm, absolutely. Next Tuesday is the 19th annual TSMC Technology Symposium keynoted of course by the Chairman, Dr. Morris Chang.

Join the 2013 TSMC Technology Symposium. Get the latest… Read More