You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

Round #1 was here.

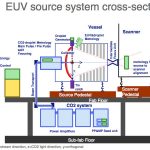

In the EUV corner were Stefan Wurm of Sematech (working on mask issues mostly) and Skip Miller of ASML who are the only company making EUV steppers (and light sources, they acquired Cymer).

You may know that the biggest issue in EUV is getting the source brightness to have high enough energy that an EUV stepper has … Read More

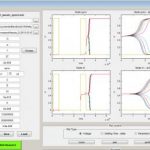

Metastability is a critical SoC failure mode that occurs at the interface between clocked and clockless systems. It’s a risk that must be carefully managed as the industry moves to increasingly dense designs at 28nm and below. Blendics is an emerging technology company that I have been working with recently, their MetaACE… Read More

TSMC announced their Q2 financial results yesterday. Revenue was $5.2B (at the high end of guidance) with net income of $1.6B. This is up 17.4% on Q1 and up 21.6% year-to-year. Gross margin is up too, at 49% which is up 3.2 points on Q1 and 0.3 points year-to-year. As usual the financial results are not directly that interesting since… Read More

In his DAC keynote last year (2012) Mike Mueller of ARM compared how much CPU was required to verify the first ARM versus one of the latest ARM Cortex CPUs. Of course the newer CPU is hundreds of times larger than the first ARM but the amount of verification required was millions of times as much, requiring ARM to construct their own datacenter… Read More

Atrenta today announced Dr Ajith Pasqual, who is the Head of the Department of Electronic & Telecommunication Engineering at the University of Moratuwa in Sri Lanka (which used to be known as Ceylon) has joined Atrenta’s technical advisory board (TAB). OK, academics join EDA company’s TABs all the time so that’s… Read More

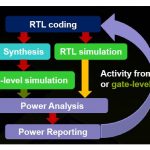

It’s a classic and creative example of design and EDA tool community getting together, exploiting tool capabilities and developing flows which add value to all stake holders including the end consumer. We know power has become extremely important for battery life in smart phones, high performance servers, workstations, notebooks… Read More

If you want to know the state of play in lithography, there is no better place than the special session on lithography at Semicon West. This year was no exception. The session was given the punchy title Still a tale of 2 paths: multi-patterning lithography at 20nm and below: EUVL source and infrastructure progress.

In the blue corner… Read More

Part 1

VLSI’s business grew healthily but it never threw off enough cash to fund all the investment required for process technology development and capital investment for a next generation fab. They made a strategic partnership with Hitachi covering both 1um process technology and a significant investment, which meant that … Read More

There is a new book out from Springer. The subtitle is actually a better description that the title. The subtitle is A Practical Guide to Synopsys Design Constraints (SDC) but the title isConstraining Designs for Synthesis and Timing Analysis. The authors are Sridhar Gangadharan of Atrenta in San Jose and Sanjay Churiwala of Xilinx… Read More

CEVA and ARM Do LTEby Paul McLellan on 07-19-2013 at 8:23 pmCategories: Arm, Ceva, IP

If you have purchased a high-end cell-phone or tablet in the last couple of years it probably has LTE, although some carriers try and blur things by showing a symbol like 4G when you are in an area that has LTE despite the fact that your phone does not support it. Don’t you love cell-phone marketing? Talking of which, if a camel … Read More