NewPath Research will describe their new method for nanoscale carrier profiling in semiconductors on May 19[SUP]th[/SUP] at the Annual SEMI Advanced Semiconductor Manufacturing Conference (ASMC) in Saratoga Springs, NY. This new method is intended to fill the gap that has been addressed in the Roadmaps for the semiconductor… Read More

Tag: semiconductor

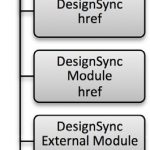

Flexible Integration System for IPs into SoC

The number of IPs with growing complexity and heterogeneity is ever increasing (counting into hundreds) to be integrated into a single SoC. It’s not possible to have them all available at once and in a single repository for the integration engineers to assemble all of them together and integrate into the SoC. The reality is that … Read More

LSI’s Way of Faster & Reliable Electronic System Design

LSI Corporationstarted in 1980s and I had several encounters with it during my jobs in 1990s; not to forget the LSI chips I used to see in desktops and other electronic systems, and I’m happy to see LSI continuing today with more vigour having leadership position in storage and networking space. It provides highly reliable, high … Read More

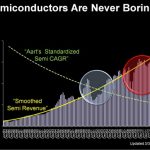

Semiconductor Cost Models: Boring But Crucial

One of the most important and underrated tasks in a semiconductor company is creating the cost model. This is needed in order to be able to price products, and is especially acute in an ASIC or foundry business where there is no sense of a market price because the customer and not the manufacturer owns the intellectual property and … Read More

Designing Change into Semiconductor Techonomics

Every industry has famous thought leaders that can summarize where we’ve been and then paint a picture of where we’re headed towards in the future. Often they make statements that become industry expressions, like “Moore’s Law” or the “Internet of Things”. I think that if Synopsys… Read More

FinFET & Multi-patterning Need Special P&R Handling

I think by now a lot has been said about the necessity of multi-patterning at advanced technology nodes with extremely low feature size such as 20nm, because lithography using 193nm wavelength of light makes printing and manufacturing of semiconductor design very difficult. The multi-patterning is a novel semiconductor manufacturing… Read More

Secret of TI’s Success in Analog & Embedded Space

Since I started looking at the ways Texas Instrumentsworks through its strategies, my belief is getting firmed up that this is one company which can always sail through rough waters during downturn and reap rich benefits during upturn. They regularly review their strategies and can predict ahead of time when the water is about … Read More

Strong 2014 for Semiconductor Equipment and CapEx

Spending on semiconductor manufacturing equipment is headed for healthy growth in 2014. The latest data from SEMI and the Semiconductor Equipment Association of Japan (SEAJ) shows March 2014 three-month-average billings for semiconductor manufacturing equipment were up 16% from February 2014 and up 31% from a year ago. Bookings… Read More

Another Intel Slide Debunked!

This was one of the most memorable keynotes I have seen, absolutely. Probably because it supports my belief that the infamous Intel slide that “projected” Intel will continue a linear manufacturing cost per transistor improvement at 14nm and 10nm is pure marketing fluff. Even more interesting, according to Intel, other semiconductor… Read More

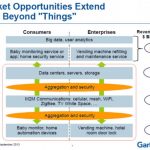

Will IoT Drive the Next Semiconductor Revolution?

To further my quest to comprehend the latest trends in the semiconductor industry continues, I spent the morning with SEMI at the “The Silicon Valley Breakfast Forum: Internet of Things (IoT) – Driving the Microelectronics Revolution” seminar. I’m a big fan of the breakfast seminar concept. I’m up early anyway and it is … Read More